https://www.bit-tech.net/reviews/tech/memory/the_secrets_of_pc_memory_part_3/5

DDR2 台式机模块由 240 针连接接口组成。

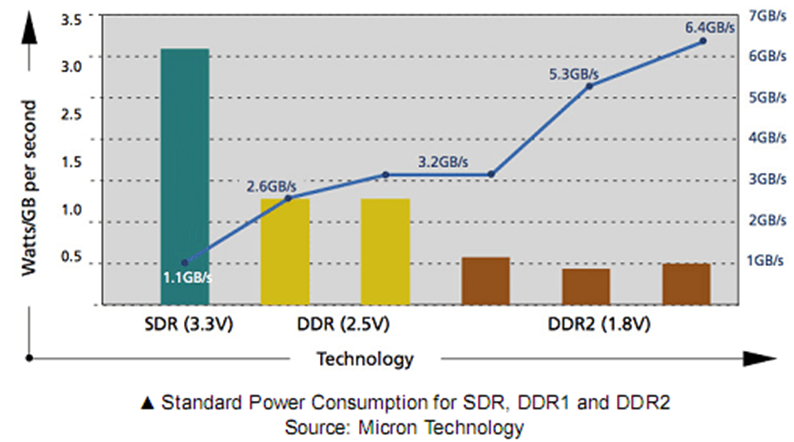

JEDEC 定义的 DDR2 工作电压为 1.8V,然而,一些厂商生产的高性能模块可在高达 2.4V 的电压下运行,并且仍然提供保修。与之相反,一些廉价模块缺乏良好的散热,为了长期可靠的运行,需要主动降低电压。

我们最近就更高的 DRAM 电压及其对寿命的影响向镁光科技计算部门高级市场经理 Brett Williams 进行了咨询。例如,我们询问了一个典型的 2.0V 电压运行的内存模块;“ [它] 的寿命实际上会比 1.8V 模块短。现在,当我说‘寿命短’时……这可能会或可能不会成为您的顾虑。在 1.8V 电压下,该模块可能可以使用长达 200 年。在 2.0V 电压下,它可能可以使用长达 10 年。但您的系统很可能会在三到五年后就被丢弃:更换内存或升级。 ”

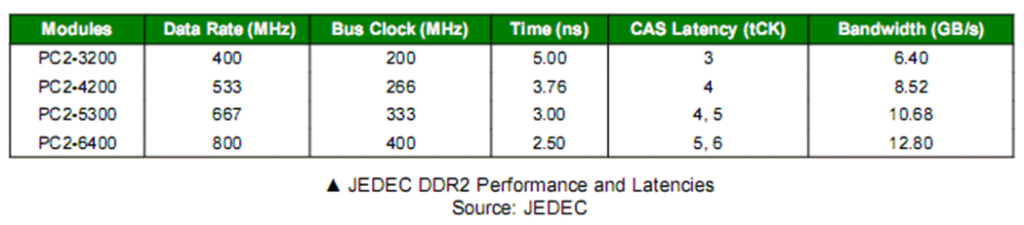

JEDEC 规定 DDR2的最高工作频率是 800MHz,因此超过 800MHz 的速度被认为超出了行业标准,需要主板特别支持。

需要注意的是,JEDEC 规范更关注“安全”冗余度。这是为了让所有的符合 JEDEC 标准的 RAM 能够适配最广泛的主板和芯片组,因此JEDEC DDR 标准更多地关注信号可靠性而非内存速度。

以瓦特/千兆字节/秒为单位的功率与吞吐量比的提高是一个积极的趋势,但许多 DDR2 台式机主板(BIOS)和内存(SPD)在出厂时就已预编程为在 1.85V 至 1.95V 的电压下运行,以应对更广泛的稳定性问题。

值得一提的是,镁光公司推出的一类特殊 1,066MHz DDR2 DRAM 原生电压为 1.8V,但仍符合 JEDEC 的要求。通常只有 800MHz 内存的额定电压为 1.8V,但这是 DDR2 市场上唯一一款原生 1,066MHz DRAM,因此特别适合以 1,066MHz 内存速度运行并可超频的 AMD 新款 Phenom CPU。Brett Williams 解释了美光公司如何通过“大幅提升利润率”实现这一目标。他告诉我们,美光公司的 D9 基本上采用了比许多竞争对手更先进的制造工艺:美光公司采用 78nm 工艺,而其他公司采用 95nm 工艺。“正是工艺和设计技术的结合,帮助美光公司实现了更高的内存频率,同时保持了最宽的信号传输裕度。 ”镁光科技的 Kirstin Bordner 为我们提供了需要注意的 D9 特定标识符,这些标识符指示 1.8V 1,066MHz DRAM。

- D9HCD MT47H64M8B6-25:D

- D9GKX MT47H64M8B6-25E:D

- D9GMH MT47H64M8B6-3:D

对称 T 型分支拓扑

PC 内存的秘密:第 3 部分

https://www.bit-tech.net/reviews/tech/memory/the_secrets_of_pc_memory_part_3/6

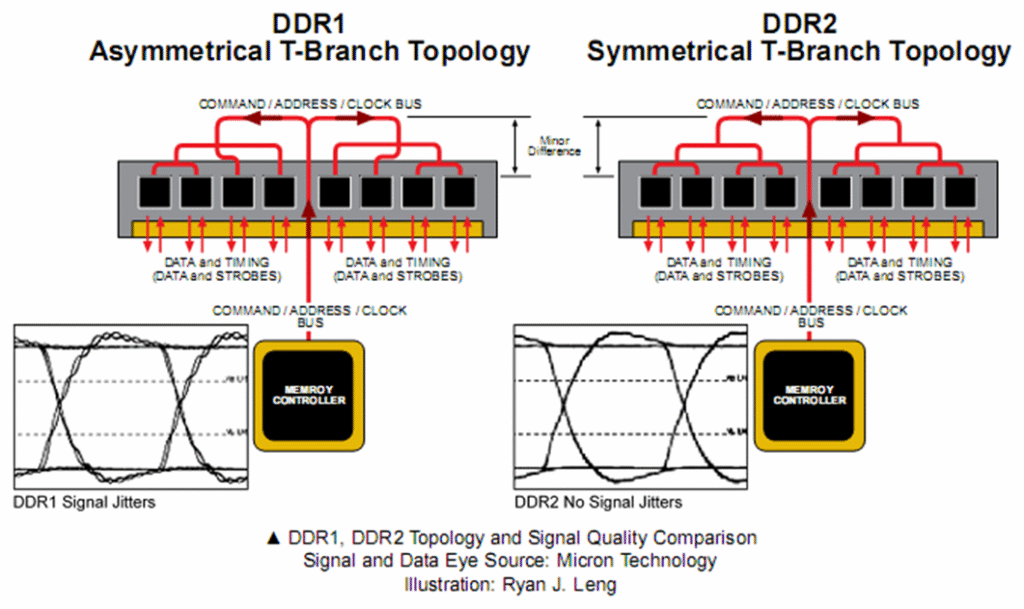

DDR2 与 DDR1 共享类似的架构,称为 T-Branch 拓扑。然而,DDR2 与上一代产品的不同之处在于它采用了对称设计。因此,每个 DRAM 芯片的命令、地址和时钟总线完全均衡,从而提高了高频信号的质量,因为更好的对称性可以降低信号抖动。

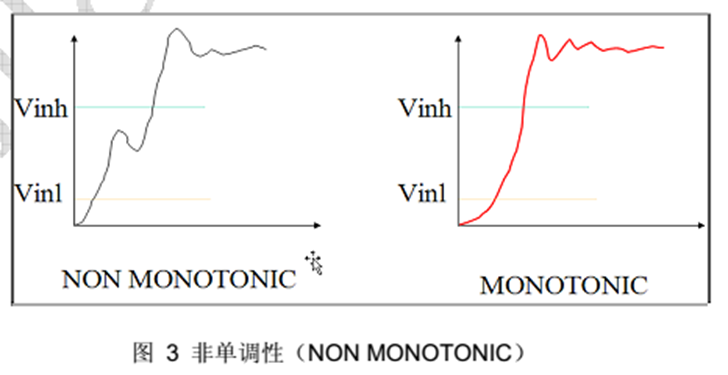

这种设计在减少 SDR 和 DDR1 总线拓扑中常见的非单调性信号(non-monotonic signal behaviour)行为方面取得了重大改进。

LAB-Z注释:非单调性(non monotonic)问题指的是信号在上升过程中出现了部分下降的情况【参考1】

绝大多数非单调性都是由复杂的信号拓扑造成的。在一个CPU或DSP的本地总线上,非单调性问题最常见。非单调性按表现形式可以分为两种:回钩和台阶。

对于一个沿有效的时钟来说,信号沿上的回钩和台阶是致命的。因为一个非单调性的时钟沿,可能被接收端认作多个有效沿,或在器件内部产生亚稳态,导致时序逻辑的功能错误。对于数据来说,非单调性的危害主要是造成时间裕量的减少,这也是复杂的总线系统往往需要进行时序仿真的原因之一。

参考:

T-Branch 仍然会导致较长的命令-地址-时钟总线和较短的数据总线之间出现时序偏差。这是因为命令-地址-时钟 T-Branch 总线具有多个分支,而数据总线则是直接连接。这在 DDR2 下不是一个大问题,但在 DDR3 速度等级中已得到解决。

数据预取

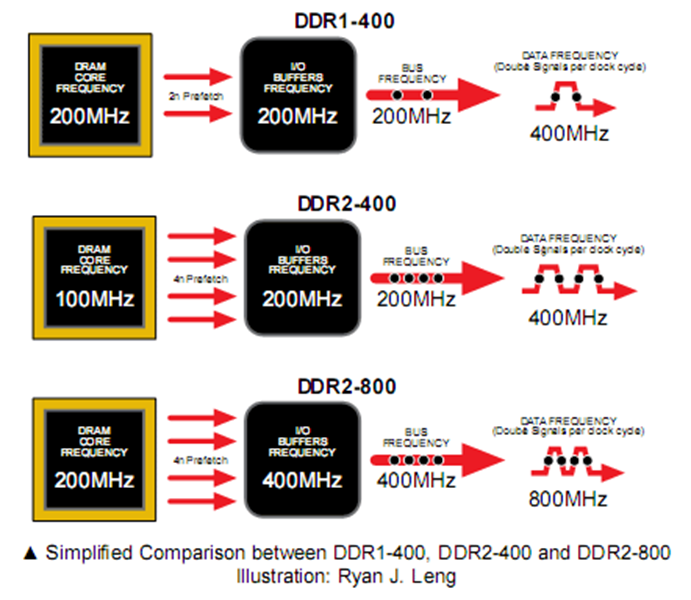

DDR2 采用“4n 预取”设计,而非 DDR1 的“2n 预取”。在每个周期,它能够将来自内部存储库的 4 位数据排列到 IO 缓冲区中,然后再通过数据总线传输出去。

据 JEDEC DRAM 委员会成员、前 ATI Technologies(现 AMD)成员 Joe Macri 介绍,4n-Prefetch 架构的主要目的是降低 DRAM 核心频率以满足更高数据速率的需求。这样,DRAM 核心就能以数据总线频率的四分之一运行。

这种设计的直接优势在于能够维持相对成熟的制造工艺,而无需进行大规模的重新设计。它能够缓解 DDR2 芯片(尤其是具有更高数据速率和密度的芯片)的产能提升和良率压力。