https://www.bit-tech.net/reviews/tech/memory/the_secrets_of_pc_memory_part_4/3

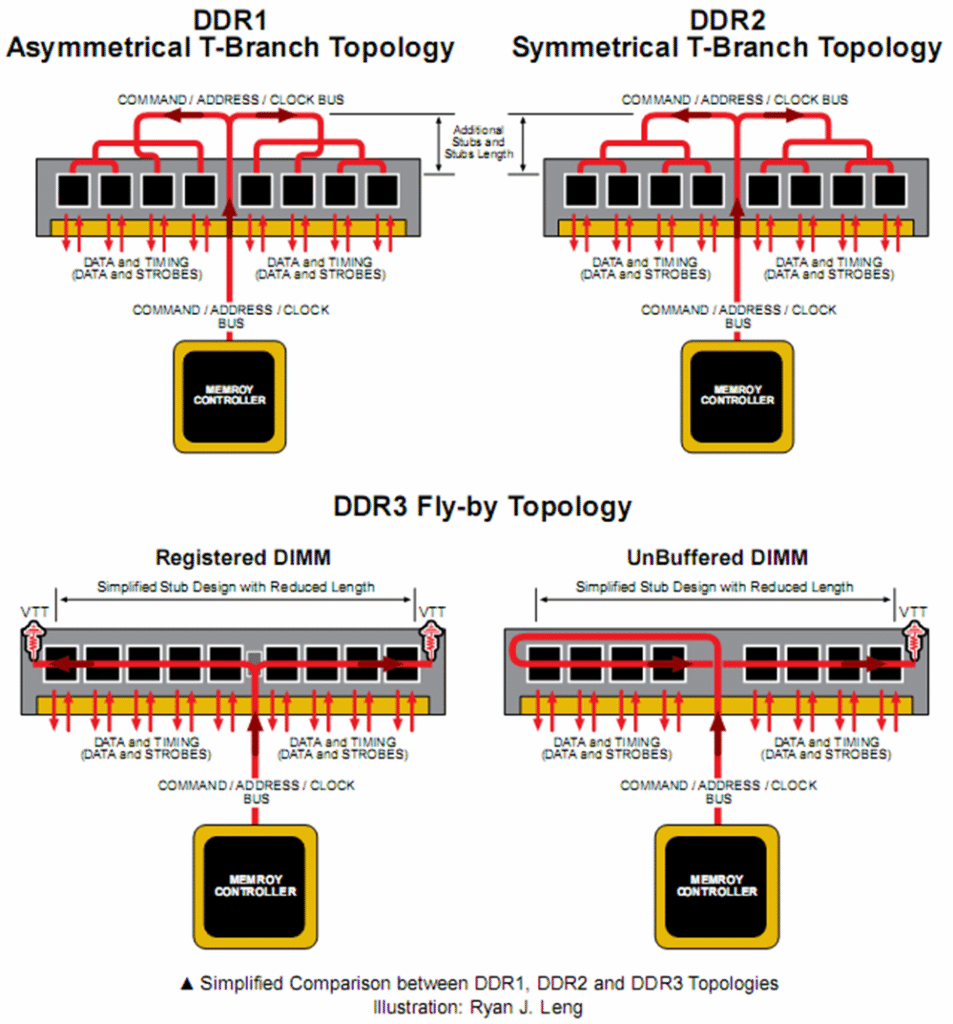

为了在更高速度等级下获得更佳的信号质量,DDR3 采用了所谓的“Fly-by”架构来传输命令、地址和时钟信号。这有效地减少了 DDR2 T-Branch 架构中的短截线数量和信号长度,使其设计更加简洁、简洁。Fly-by 拓扑通常将内存模块上的 DRAM 芯片串联起来,并在线性连接的末端设置一个接地端接点,用于吸收残余信号,防止其沿总线反射回来。

我们最近采访了镁光公司的应用工程师 Aaron Boehm,了解 Fly-by 拓扑对 DDR3 的重要性。他表示,Fly-by 设计“在 DDR3 中非常重要。采用 Fly-by 拓扑的最大优势之一或许在于:能够实现更快的信号斜率。这为我们提供了更好的眼图数据,这在 DRAM 中非常重要。 ”

Fly-by 架构的实际应用 资料来源:RAMBUS

Boehm 强调:“如果没有 Fly-by 设计,DDR3 将无法发送信号。 ” 实施这种新架构是为了避免 DDR2 在更高速度下出现的 T-Branch 限制,因为“所有寻址命令都必须在一个时钟周期内到达 DRAM。Fly-by 拓扑结构可以解决这个问题。如果开始提高速度,那么在一个周期内将这些信号发送到 DRAM 就相当困难了。 ”

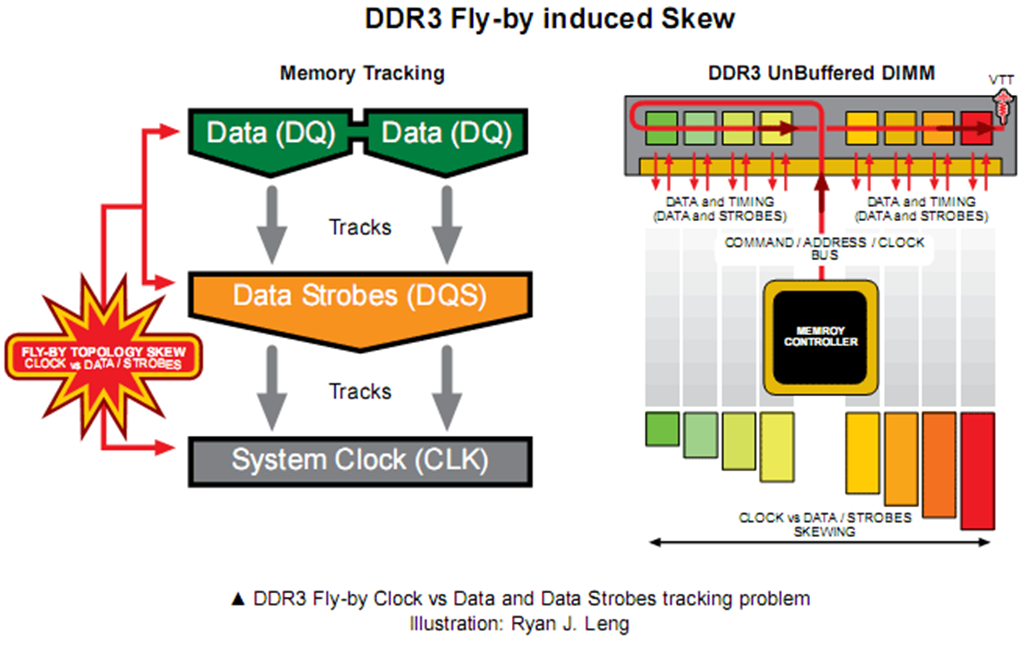

尽管 Fly-by 拓扑结构有诸多优势,但也增加了复杂性;命令-地址-时钟总线与 DRAM 的顺序 Fly-by 连接会导致沿线每个 DRAM 的数据总线时钟偏差增加。简而言之,命令-地址-时钟总线信号沿线传输的延迟会增加。

读写分级

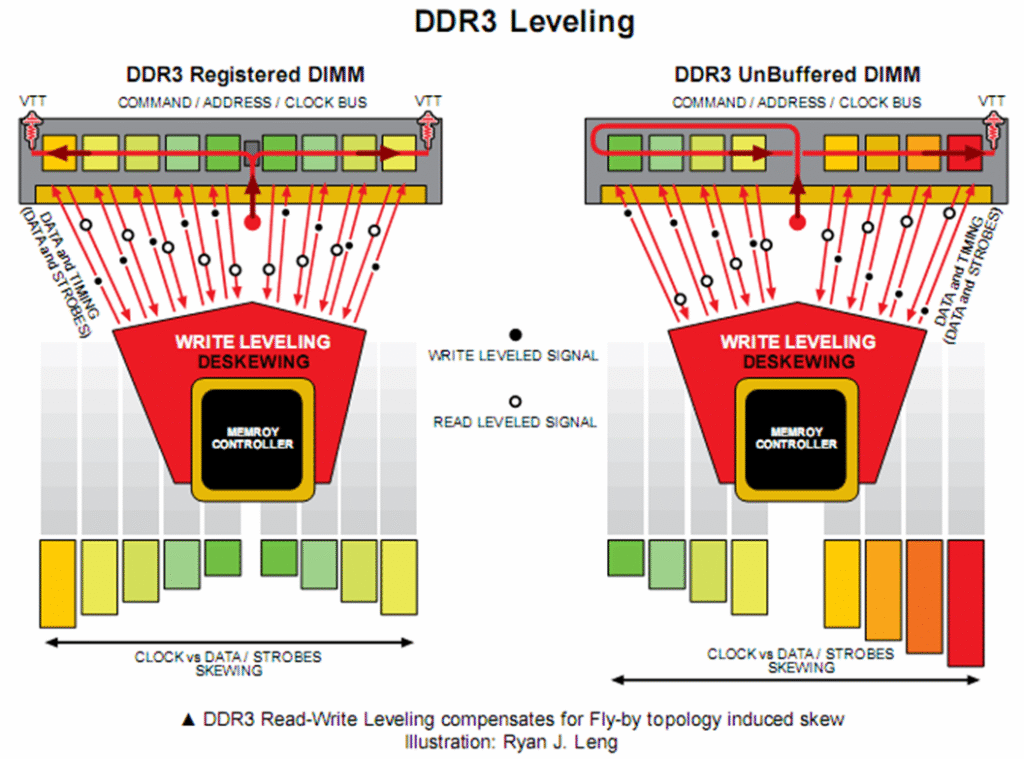

DDR3 内存控制器内置了读写均衡功能,以补偿这些时钟偏差问题。Boehm解释了新拓扑结构的问题:“时钟、命令和地址都以‘Fly-by’方式路由到每个 DRAM,而包含选通信号的 DQ [数据] 总线的路由方式更类似于 T 分支。命令、地址和时钟到达每个 DRAM 的时间略有不同,而 DQ 信号到达的时间大致相同。因此,在采用飞越方式的每个 DRAM 中,DQ 总线和时钟之间存在固有的偏差,这会导致问题,您必须通过(在另一端)进行去偏差来解决,以使一切重新对齐。

“这就是 DDR3 中写入均衡的用武之地。您所做的就是稍微延迟 DQ 总线,使其与时钟同时到达每个 DRAM。内存控制器会动态地将每个 DRAM 芯片的数据-数据选通 (DQ-DQS) 与时钟 (CK) 对齐。

这通过简单的”问候-应答”(Hello-and-Respond)反馈分析完成。一旦确定了每个 DRAM 芯片的延迟或偏差量,内存控制器就可以轻松地在后续活动中补偿该问题。DDR3使用新的Multi-Purpose Register (多用途寄存器,MPR) 进行信号调平处理;这会在初始化期间生成用于校准的预定数据模式。MPR 通过动态调整数据选通使其尽可能靠近数据眼的中心来帮助内存控制器校准。

当内存控制器处于写入均衡模式时,至少一个数据位必须通过 x4、x8 或 x16 的 DRAM 配置将均衡反馈传送到内存控制器。校准完成后,内存控制器将启动写入均衡禁用序列。

均衡过程也以另一种方式进行;顾名思义,读取均衡会在读取周期内将数据总线与命令-地址-时钟总线对齐。完成内存控制器均衡校准程序后,内存将恢复到标准操作模式。

类比:多个机场接送

想象一下,你需要接八位乘飞机来参加节日团聚的亲戚。每个人到达的时间都不一样。

起初你并不知道每个人的日程安排,所以你必须在他们离开家之前给他们打电话。打电话给每个人确认他们是否到达,正是内存控制器中的多用途寄存器 (MPR) 的功能。

一旦你知道每个人的到达时间,你就可以安排各自的接机时间,最早的在最前,最晚的在最后。你是数据 (DQ),你的车是数据选通 (DQS),机场是内存模块,亲戚们是通过 Fly-by 路径飞来的命令-地址-时钟信号。每个人都会到达不同的登机口,代表 DRAM 芯片。

动态片上终端 (ODT)

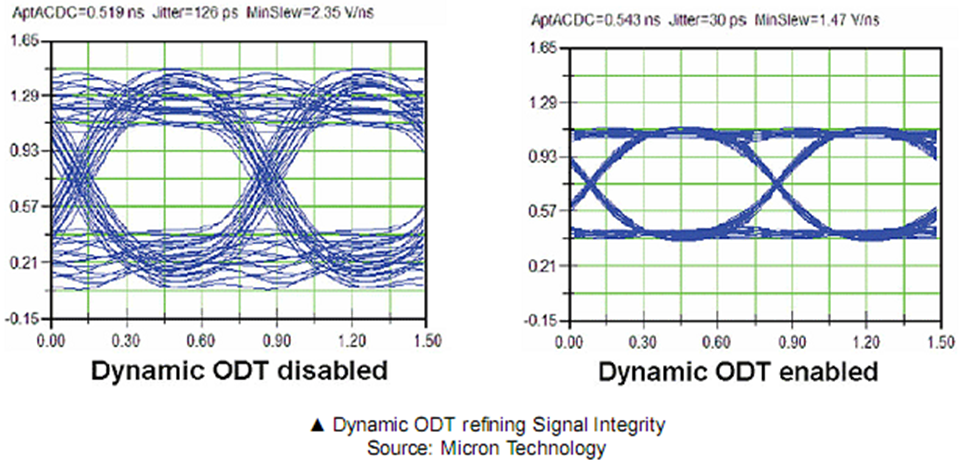

DDR3 扩展了 DDR2 的片上终端电阻设计,通过增加额外的灵活性,可以优化不同条件下的终端电阻值,从而管理终端电阻的功耗。

在读写操作期间未被访问的内存模块,可以使用 30 或 40 欧姆的低阻抗值来终止数据总线。在写入操作期间,最佳终端电阻可以更改为约 60 或 120 欧姆的高阻抗值。

镁光公司的 Todd Farrell 表示:“动态 ODT 允许 DDR3 SDRAM 设备在向不同模块发出写入命令之间无缝更改终端电阻值。此功能在 DDR2 SDRAM 系统中不可用,因为在同一设备上更改终端电阻值时需要总线空闲时间。 【这句话含义我不理解】”

动态 ODT 可根据不同情况调整终端电阻值,将干扰噪声降低到更易于管理的水平,从而进一步提升信号完整性。这使得内存能够以比 DDR2 更高的速率运行。

ZQ 驱动器自校准

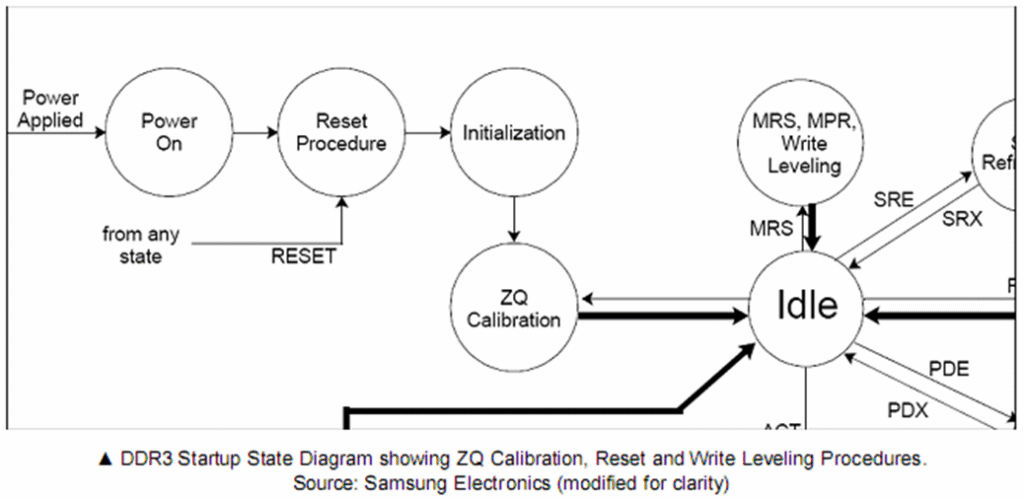

此功能有时称为“ZQ 校准”,用于增强阻抗值校准并实现更严格的公差。这是一项重要的改进,涉及分配所谓的“ZQ”引脚以实现片上驱动器校准功能。ZQ 引脚位于 DRAM 芯片本身上,因此有时可以将其称为球栅阵列 (BGA) 封装中的“ZQ 球”。ZQ校准在两个级别运行:首先,它在任何主要内存操作之前的启动序列中使用 – 这称为“ZQ 长校准”或 ZQCL。启动校准通常需要更长时间,并且在 DDR3 写入均衡之前。

第二个 ZQ 校准称为“ZQ 短校准”或 ZQCS。它有时被称为“跟踪校准”,因为它发生在整个内存操作周期中,但所需的时间比启动阶段的校准要少。

实施跟踪校准是为了在整个内存操作过程中降低在较高频率下信号时序严重不准确的可能性。通过在正常运行期间随着电压和温度的上下漂移重新校准阻抗值,可以显著减少阻抗不连续的问题。

总而言之,ZQCS 持续跟踪和补偿电压和温度 (PVT) 的变化,以实现最佳数据眼,从而实现最佳数据传输。ZQ 引脚连接到一个高精度外部电阻器,该电阻器用于高清调整输出驱动器的“导通”阻抗和 ODT 阻抗。ZQ校准是 DDR3 的一个重要特性:随着在给定时间内挤入更多数据以实现更快的传输,DDR3 可用的裕度更小。如果没有 ZQ 校准,DDR3 的可靠性将大大降低。

复位功能

DDR3 引入了异步复位功能,该功能由内存控制器从外部启动。复位信号将强制 DRAM 进入明确定义的非操作状态。这是一个低调却又极其关键的功能。

复位功能会清除 DRAM 中的所有状态和数据,而无需单独复位每个 DRAM 或关闭模块电源。当内存控制器尝试将内存恢复到已知状态时,这可以节省时间和功耗。一旦复位被激活,内存将完全重新初始化,并且可以在任何周期的任何时间激活复位。

在内存启动功率上升期间,复位会被激活,直到内存功率达到稳定状态——这确保后续校准不会基于不可靠的功率状态。复位与 ZQ 校准协同工作,在任何周期,一旦复位功能被激活,ZQ 校准长 (ZQCL) 就会发挥作用。这将确保在数据传输开始之前,时序精度和信号质量处于最佳状态。

一些内存设计师在 JEDEC 上多次讨论并要求实现此功能,但直到 DDR3 出现,无需任何特定分配的 DRAM 引脚才使重置功能成为可能。

DDR3 及后续产品面临的挑战

在2007年电子设计大会DesignCon上,Altera公司发表了一篇关于校准技术和DDR内存未来发展状况的论文。论文指出:“尽管每一代内存的性能都会翻一番,但内存的不确定性并不会以同样的速度下降。 ”

我们最近就1600MHz及更高频率的DDR3内存设计挑战向镁光科技进行了咨询。应用工程师Aaron Boehm表示:“随着每一代DRAM的推出,设计难度都越来越大,因为我们的芯片尺寸不断缩小,速度不断提高,电压却不断下降。获取DRAM内部和外部的清晰信号变得更加困难。总线架构极具挑战性,信号走线越紧密,串扰问题就越多。 ”

Boehm继续强调,“电压降低后,很难获得良好清晰的信号边沿。因此,我认为随着我们不断进步,满足这些速度要求将变得越来越具有挑战性。 ” 从根本上说,当内存速度提高时,可用的余量也会随之减小。

内存系统由内存模块、主板和 CPU 组成。计算机内存系统不能仅仅被视为单个部件,而应该包含主板上的整个内存子系统。因此,内存性能和超频高度依赖于所有这些组件在越来越严格的容差下完美运行。

这给 DRAM 和内存模块制造商带来了一个新问题:随着内存速度的提升,实现组件兼容性变得越来越困难,“ ……尤其是在市面上存在各种主板设计的情况下。这非常困难,因为你试图在一个很多情况下都无法控制的环境中运行。即使他们想要极快的速度,他们也在试图降低 PCB 或主板的成本, ”Boehm说。

随着每一代 DDR 技术的发展,超频收益都在递减,这是意料之中的事情。

LAB-Z注释:至此,PC内存的秘密系列已经翻译完毕,后面我会继续介绍内存相关知识。