《PC 内存的秘密 第一部分》 本文来自

https://www.bit-tech.net/reviews/tech/memory/the_secrets_of_pc_memory_part_1/3/

第三章 DDR内存家族

计算机内存层次结构 不同类型的内存在计算机工程总体方案中发挥着不同的作用。它们根据用途、速度、复杂性和制造成本进行分类。

通常,更快的内存设计和制造成本更高。因此,它们的容量通常更有限。反之亦然,较慢的内存和存储系统几乎总是具有更大的容量。

计算机内存层次结构是一种金字塔结构,通常用于说明不同内存类型之间的显著差异。此图及其变体可在互联网上的各种参考网站(如维基百科)上找到。

此处所示的计算机内存层次结构版本代表了标准台式计算机中各种内存技术之间的不同性能水平。

DDR 内存系列

双倍数据速率的SDRAM (Double Data Rate SDRAM,缩写DDR) 是 1993 年推出的同步动态随机存取内存(synchronous dynamic random-access memory SDRAM ,缩写SDR) 技术的一次革命性进步。随着SDR技术在 1999 年达到极限,DDR 技术被设计为接下来十年的解决方案。

描述 DDR 内存规格的方法有两种。一种使用实际的 DRAM 芯片规格;另一种使用内存模块规格。这两种方法有时可以互换使用,但随着研究的深入,您会发现并非所有内存即便标称着相同的规格,彼此之间还是存在着差异。

DDR 各代之间的主要区别

除了物理差异之外,每一代 DDR 之间都有基础性的区别。每一项技术进步的目标都是为了解决更高性能相关的问题或副作用,例如信号噪声、偏移、抖动、时序不准确、干扰等等。

前几代中也会存在上述问题,只是在较慢的速度下这些问题通常不会导致严重的问题。而当内存的速度提升之后,就需要新技术来缓解高速信号的信号不确定性。更高的性能需要更严格的容差。

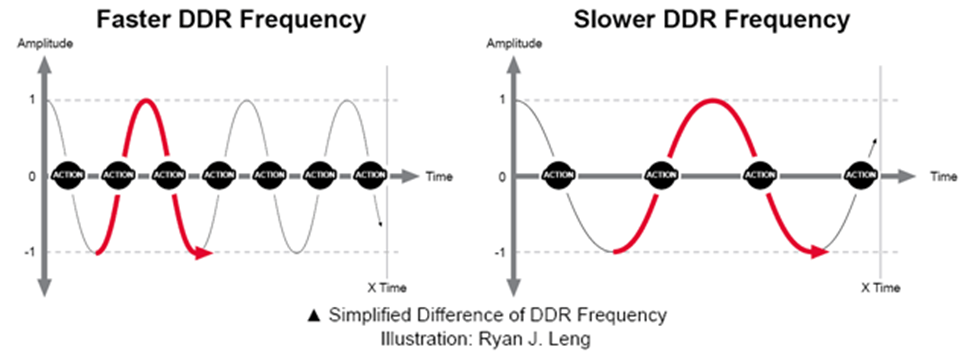

SDR 对内存数据采样发生在时钟的每一个上升沿,DDR 则是在上升沿和下降沿,因此,速度可以做到两倍。

时钟周期是指波形从波谷到达波峰再次到达波谷所需的时间,此处显示的正弦波信号实际形状介于方波和正弦波之间。在一个时钟周期内,时钟上升沿发送一次数据,下降沿发送一次,这样就实现了一个时钟周期发送2次数据。这是 DDR 技术的关键。

从下图也可以看到,同样的时间内,频率越高(周期越小),可以发送的数据也会越多:

下面表格是 DDR1-3 的一些简单对比:

| Features | Unit | DDR1 | DDR2 | DDR3 |

| Connecting Pins | ||||

| DIMM | 184 | 240 | 240 | |

| SO-DIMM | 100 200 | 200 | 204 | |

| Registered DIMM | 184 | 240 | 240 | |

| Mini-DIMM | – | 244 | – | |

| Micro-DIMM | 172 | 214 | – | |

| Packaging | 60-pin TSOP2 / 60-pin FBGA / LQFP | 60/84-pin FBGA | 78/96-pin FGBA / FBGA with Mirroring | |

| Length | mm | |||

| DIMM | 133.35 (5.25) | 133.35 (5.25) | 133.35 (5.25) | |

| SO-DIMM | 66.7 (2.625) | 66.7 (2.625) | 66.7 (2.625) | |

| Registered DIMM | 133.35 (6.25) | 133.35 (6.25) | 133.35 (6.25) | |

| Mini-DIMM | – | 82 (3.23) | 83 (3.23) | |

| Micro-DIMM | 54 (2.13) | 54 (2.13) | 54 (2.13) | |

| Dram Core Freq | MHz | 100 – 200 | 100 – 200 | 100 – 200 |

| Topology | Asymmetric T-Branch (T-Daisy) | Symmetric T-Branch | Fly-By with Termination | |

| JEDEC Classified Data Rate | DDR-200/266/333/400 | DDR2-400/533/667/800 | DDR3-800/1066/1333/1600 | |

| Prefetch Width | bits | 2 | 4 | 8 |

| Bandwidth (theoretical) | GB/s | |||

| Single-Channel | 1.6 / 2.13 / 2.67 / 3.2 | 3.2 / 4.26 / 5.34 / 6.4 | 6.4 / 8.53 / 10.67 / 12.8 | |

| Dual-Channel | 2.2 / 4.26 / 5.32 / 6.4 | 6.4 / 8.52 / 10.68 / 12.8 | 12.8 / 17.06 / 21.34 / 25.6 | |

| Module Capacity | 128MB – 1GB | 256MB – 4GB (8GB) | 512MB – 8GB (16GB) | |

| Number of Banks | 4 | 4 or 8 | 8 | |

| Read/Write Leveling | No | No | Yes | |

| Supply Voltage | Volts | 2.5 +/- 0.2 | 1.8 +/- 0.1 | 1.5 +/- 0.075 |

| Max Operating Temp | ºC (ºF) | 85 (185) | 85 (185) | 85 (185) |

| I/O Width | x4 / x8 / x16 | x4 / x8 / x16 | x4 / x8 / x16 / x32 | |

| DIMM Calibration Resistors | No | No | Yes | |

| Burst Length | 2, 4 | 4, 8 | 4 (Burst Chop), 8 | |

| RHoS | Vendor Dependent | Vendor Dependent | Vendor Dependent | |

| Latency | ||||

| CAS Latency (CL) | tCK | 2, 2.5, 3 | (2), 3, 4, 5, 6 | 5, 6, 7, 8, 9, 10, (11) |

| Additive Latency (AL) | tCK | – | 0, 1, 2, 3, 4 | 0, 1, 2 |

| READ Latency (RL) | tCK | CL | CL+AL | CL+AL |

| WRITE Latency (WL) | tCK | 1 | RL-1 | 5, 6, 7, 8 |

| CAS Write Latency (CWL) | tCK | – | – | 5, 6, 7 |

| DQ Timing | ||||

| READ | DLL aligns DQ, DQS to CK | DLL aligns DQ, DQS, DQSb, RDQS to CK | DLL aligns DQ, DQS, DQSb to CK | |

| WRITE | Setup / Hold to DQS | Setup / Hold to DQS DQSb | Setup / Hold to DQS DQSb | |

| Data Strobes | Single-ended data strobe | Single-ended or Differential data strobe | Differential data strobe with WRITE leveling | |

| Termination | Motherboard Chipset | On-Die Termination | Dynamic On-Die | |

| Driver Calibration | No | Off-Chip Driver (OCD) | On-Chip Self-Calibration with ZQ pin | |

| DQ Driver Strength | Narrow Envelope | 18 +/-3 Ohms, OCD Calibration | 30-40 Ohms, ZQ pin Calibration | |

| Interrupts | Yes | Wr-Wr, Rd-Rd (4n only) | Burst Chop for Rd and Wr | |

| Reset Function | No | No | Yes (Asynchronous) | |

| Thermal Sensor | No | SO-DIMM (on DIMM), FB-DIMM (on Die) | SO-DIMM (on DIMM), FB-DIMM (on Die) | |

| Automatic Self Refresh (ASR) | Supported | Supported | Supported | |

| Temp. Compensated Self Refresh (TCSR) | Supported | Supported | Supported | |

| Self Refresh Temp (SRT) | <= 85 ºC | <= 95 ºC | <= 85 ºC, <= 95 ºC | |

| Partial Array Self Refresh (PASR) | Supported | Supported | Supported | |

| Deep Power Down (DPD) | Supported | Supported | Supported | |

| Clock Stop Mode | Supported | Supported | Supported |

来源: JEDEC, Altera Corporation, Elpida Memory, Infineon Technologies, Kingston Technology, Micron Technology, MOSAID Technologies, Qimonda, Rambus, Samsung Semiconductor, Via Technology