堆叠方法通常用于经济地增加 PC 内存的密度,即通过添加额外的层(例如芯片、IC 和/或 PCB)来实现。堆叠通常分为两种布置方式:卡叠卡和封装叠封装。

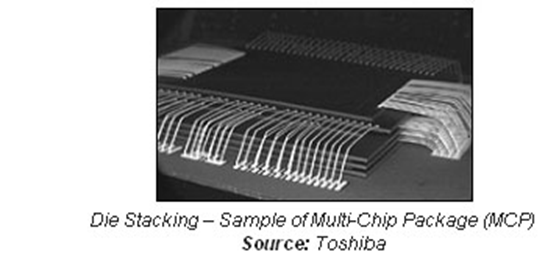

为了提高单芯片密度,BGA 芯片采用了多芯片封装 (MCP) 堆叠技术。与沿 DIMM 侧面排列多个芯片不同,每个芯片在单个芯片封装内彼此堆叠。DRAM 制造商可能拥有自己专有的晶圆减薄和微型化技术,以实现更小的封装和更高的芯片数量。

从 2007 年起,三星半导体预计将使用其专有的“硅通孔”(TSV)和全 DRAM 堆叠配置——这种设计更简洁、更小、更快、功耗更低。然而,三星并不是唯一使用这项技术的公司,英特尔在去年春季的 IDF 上也曾演示过Terascale 技术,将内存堆叠在 80 核处理器上。

当今 MCP 技术的问题在于,不同层的 DRAM 通过脆弱的引线键合连接。这种配置要求层与层之间有几十微米深的垂直间隙,而且这种连接还需要封装板上几百微米宽的水平间距来连接芯片之间的引线。这种技术精度成本高且很难控制质量,因为数百条引线中一条短路都很难找到,更难纠正。

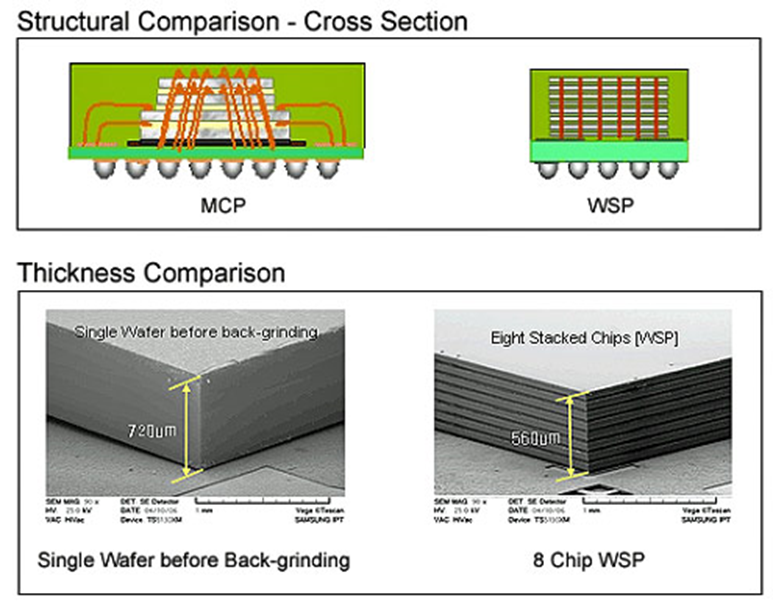

三星晶圆级堆叠封装 资料

来源:Samsung Electronics

据三星称,其晶圆级工艺堆叠封装 (WSP) 技术“通过激光切割形成微米级孔洞,这些孔洞垂直穿透硅片,并将内存电路与铜 (Cu) 填充物直接连接,无需额外的间隙和超出芯片边缘的导线。这些优势使三星的 WSP 能够显著缩小尺寸并实现更薄的封装。”

最新成果是三星改进的 4GB DDR2 内存模块,其性能更加出色。每个芯片将包含四层 512 兆位 DRAM,使每个芯片的密度达到 2 千兆位。升级后的 TSV 技术预计将用于 DDR3。

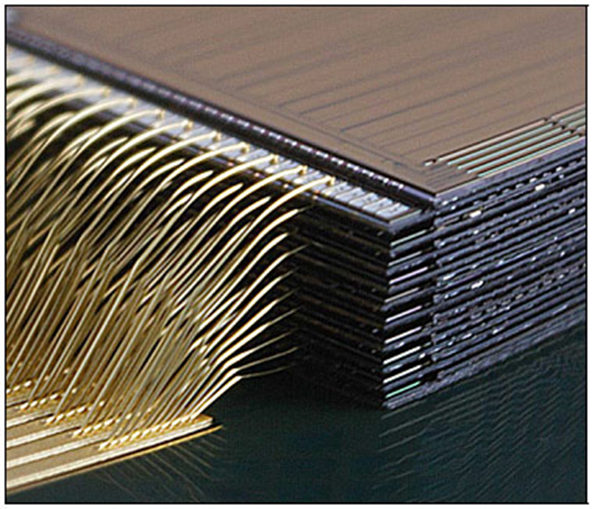

全球最薄的 1.4 毫米 MCP,配备 20 个堆叠芯片

来源: Elpida Memory

秋田尔必达存储器公司(Akita Elpida Memory)于2007年上半年成功开发出一款厚度仅为1.4毫米的MCP,其内部堆叠了多达20个芯片。该芯片采用独特的研磨技术,厚度仅为30微米,并在处理这些微型芯片、引线键合以及将树脂注入狭窄间隙以实现各层之间电气绝缘等方面也做出了创新。最重要的是,该芯片预计产量高且成本低——坦白说,这确实是一项了不起的成就。

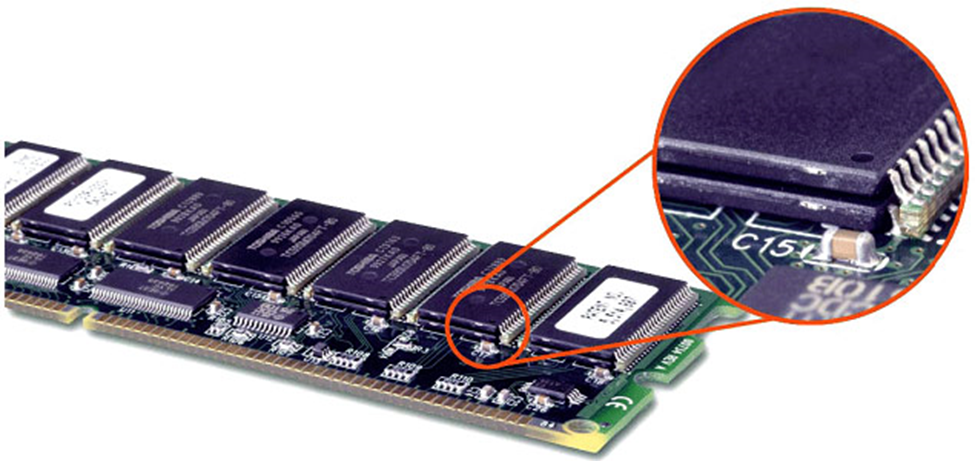

以下是一些用于增加每个模块密度的堆叠方法:

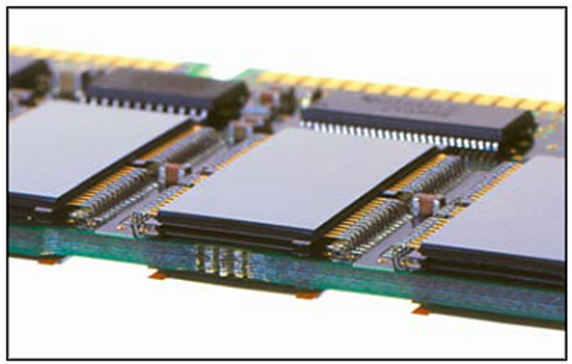

TSOP DRAM 堆叠

来源: STEC

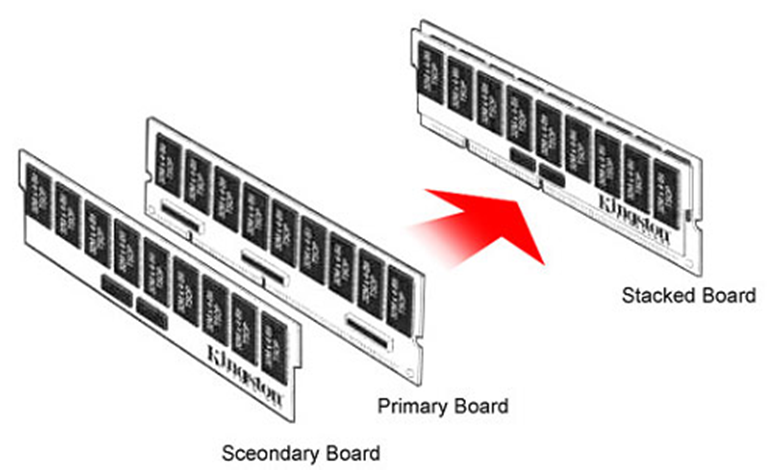

模块堆叠

来源:Kingston Memory

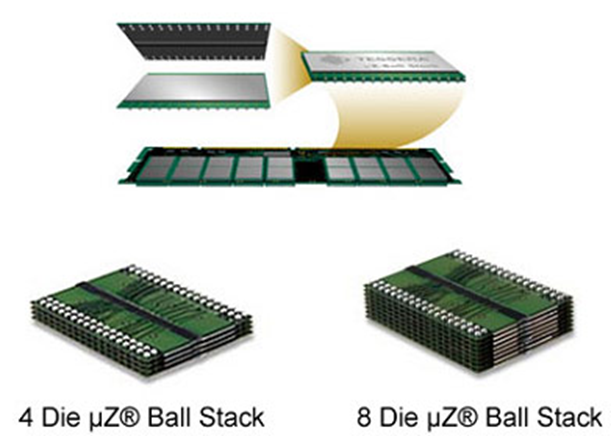

专有 BGA 堆叠

来源: Tessera

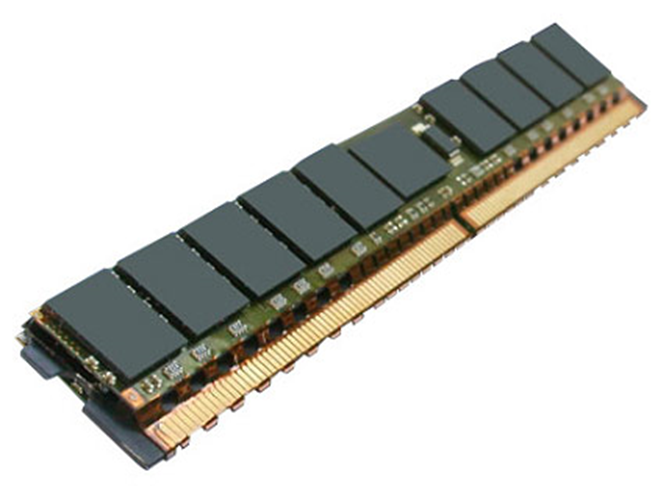

TSOP载带封装堆叠技术:芯片放置在载带上,背面暴露。

来源:Elpida Memory

SMART Modular Technologies 在其 CoolFlex DDR2 2GB 薄型模块中采用了一种名为“折叠印刷电路板”的有趣技术。该技术利用折叠 PCB 技术将内存容量翻倍,这样避免了DRAM本身的队列。与更复杂的多芯片堆叠技术相比,这是一种相对经济有效的方法。

超薄型 2GB DDR2 带折叠印刷电路板

资料来源: SMART Modular Technologies

DRAM制造

每个内存芯片封装都包含一个或多个晶圆,每个晶圆都是从一块更大的圆形硅片上切割下来的。制造过程中会进行严格的检查,以确保晶圆完美无瑕。晶圆切割完成后,会被放入封装中,并进行连接——这构成了DRAM芯片的基础。

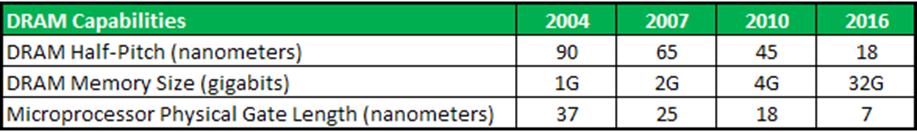

DRAM 制造的一个重要方面是晶圆制造分辨率,以纳米为单位。与 CPU 的演进一样,DRAM 技术也遵循着稳步的微型化路径,以实现更高的密度和更强大的性能。DRAM的性能与光刻制造工艺中的关键技术进步息息相关,这些进步就像 DRAM 演进时间线上的感叹号。下表列出了国际半导体技术路线图 (ITRS) 设定的 DRAM 制造工艺目标。

ITRS 的 DRAM 目标

来源:半导体行业协会

ITRS 解释说:“DRAM 半节距与连接 DRAM 位单元的金属线之间的宽度和间距相关——半节距越小,在给定面积内可容纳的 DRAM 位单元就越多……栅极长度越短,切换时间越短。”

更小的电路可以使信号传输速度更快,同时功耗更低。技术发展的每个阶段都会带来效率的提升、容量的增大以及性能特征的全面提升:这与 CPU 技术的演进非常相似。

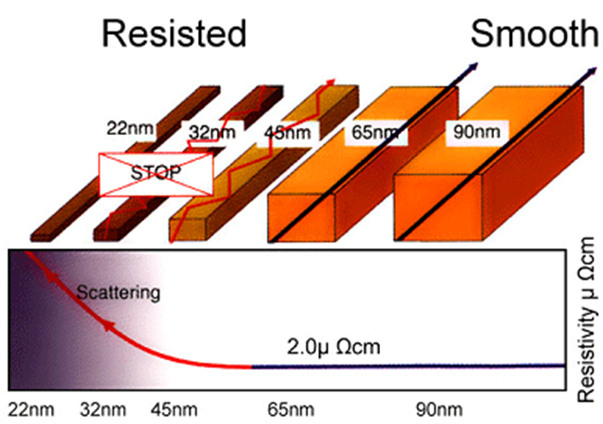

随着行业向 45 纳米制造工艺、450 毫米晶圆、45 微米晶圆厚度和 3D 芯片封装技术迈进,预计 2010 年和 2011 年将发生重大变革。当技术经历范式转变时,企业会提出许多担忧,主要涉及设备更换或改造的成本,以及某些材料在 45 纳米或更小节点的电气性能下降。

随着行业向 45 纳米及以下节点迈进,电阻和电子散射效应将会增加。随着电路尺寸的减小,电流会因为较小铜线中的较大电阻而变得更加困难,从而增加了缺陷的风险或损害了信号完整性。

ITRS 的 DRAM 目标

来源: ITPC 小组成员 Tsujimura 博士的讲座

除了提高“互连”线路的导电性外,另一种提高电流的有趣方法是降低晶体管的电阻特性。制造商利用先进的材料科学来改进基本的芯片电路。2007年,东芝通过使用不同的材料配置并在晶体管电极和硅基板之间的边界表面分散掺杂剂,使晶体管的电流提高了35%。

目前也有一些关于使用碳纳米管 (CNT) 作为基本电路和互连线的基础研究。它被认为是在2020年之前维持摩尔定律的有希望的元素之一。据Philip G. Collins和Phaedon Avouris在《科学美国人》(2000年12月刊)上报道,金属纳米管的电流密度可以比银和铜等金属高1000多倍。

首先,使用碳纳米管在一些方面具有挑战性,其制造和电路布局工艺极其复杂。人们考虑过各种制造技术,包括印刷法和生长法,但这两种技术都还非常年轻,尚未直接应用于半导体的大规模生产。2007年 5 月,镁光科技宣布推出采用 78 纳米工艺的 DDR2 和 DDR3 DRAM 芯片。凭借这种新的制造工艺,镁光公司能够将数据频率提高到 1,066MHz,同时将工作电压保持在常见的 1.8V。这是一项重大成就,因为它使 DDR2 1,066MHz 内存能够在 JEDEC 认可的 DDR2 电压标准下工作,与所有主板高度兼容,这意味着它也完全符合 AMD 新款 AM2+ CPU 的要求,这些 CPU 以 1,066MHz DDR2 内存速度运行。

使用这些 IC 构建的模块也将具有更大的超频余地,正如镁光目前的“6F2” DDR3 芯片产品所见; “镁光公司采用 78 纳米工艺和 6F2 技术,实现了迄今为止分析过的所有 DRAM 器件中最小的单元尺寸,仅为 0.0365 微米……金属-绝缘体-金属 (MIM) 电容单元设计和凹槽通道存取晶体管,使字线和位线间距均减小至 156 纳米。” 目前,所有低延迟 1,333MHz 和 1,600MHz 及以上频率的高性能 DDR3 均采用基于镁光D9 的内存芯片。

这正是核心爱好者和超频玩家寻找特定 DRAM 芯片并追踪特定内存品牌和型号的关键原因——此前,一些 DDR1 模块上使用的华邦 BH-5 和三星 TCCD 芯片也曾出现过这种情况。值得注意的是,一些制造商(例如 Corsair 和 OCZ Technology)倾向于对这些额定频率较低的高质量 DRAM 进行预超频,以便通过提高工作电压来获得更快的时钟速度。