https://www.bit-tech.net/reviews/tech/memory/the_secrets_of_pc_memory_part_3/8

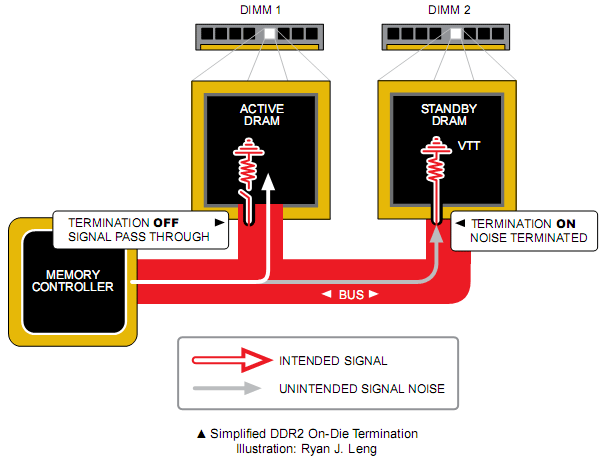

随着主板功能日益丰富,性能不断提升,保持信号完整性也变得越来越困难。当内存速度超过DDR1 之后,DDR1主板采用的电阻式终端方案无法克服信号反射问题。

内存总线频率的提升会降低信号的冗余度。压缩程度越高、电压越低的信号,其本质就越弱。虽然数据选通 (DQS)无法消除所有的抖动,但是这种设计能够减小波形边缘负面影响。

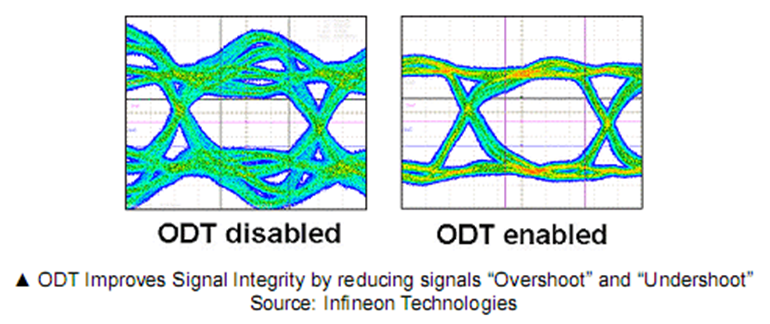

和DDR1相比,DDR2将终端电阻 (ODT)从主板上移入了内存芯片中。这样能够提高信号质量保证完整性。这不仅带来了其他好处,还降低了主板制造商的材料和测试成本。意外信号可能会从有源或无源元件反弹,但只有像 DRAM 这样的有源元件会受到不利影响。ODT 可以消除芯片级读写操作期间总线上信号回波的负面影响。

讽刺的是,如果端接过于有效,当内存时序不准确时,数据信号可能会被吸收——超频有时会导致这种数据截断内存错误。

某些主板的BIOS允许用户手动调整ODT的电阻特性,范围在50、75或150欧姆之间。根据JEDEC规范,在某些平台上,DDR2-667及更高版本的内存必须使用50欧姆。

要确定您的内存模块是否支持50欧姆,可以使用名为SPDTool的程序查看预定义的内存性能值和特性。主板设计人员需要根据各种ODT配置正确模拟和测试读写信号质量,以找到最佳数据眼孔径的要求。

模拟过程可能非常繁琐且耗时,因为它们需要根据主板阻抗和ODT设置的组合,针对不同插槽配置的众多内存模块收集数据眼孔径数据。这也是廉价主板只有两个插槽的部分原因。

片外驱动器 (OCD) 校准

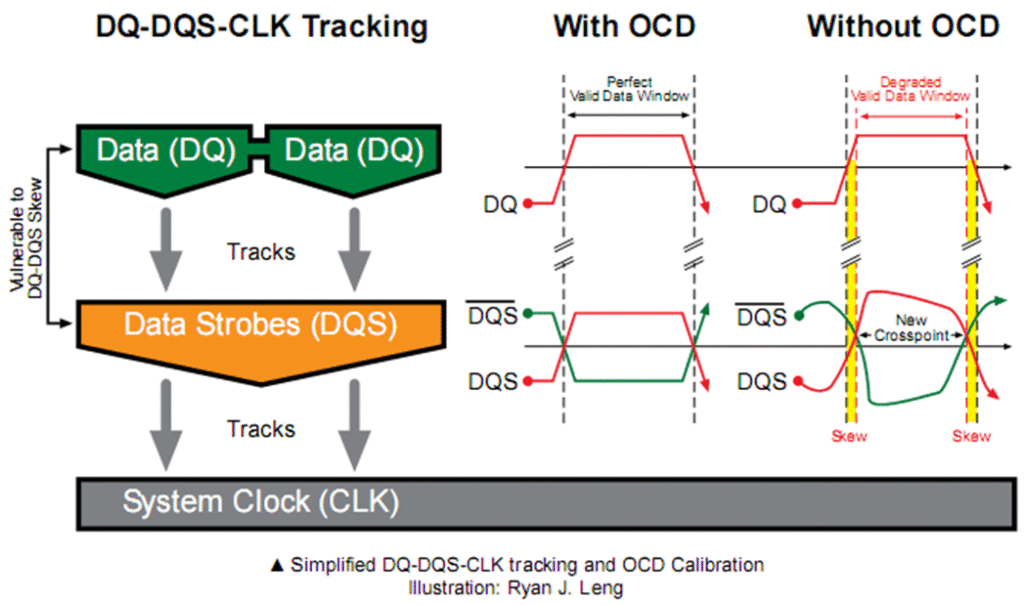

DDR2 使用片外驱动器校准来提高数据和数据选通之间的跟踪精度。OCD 校准电路用于在内存初始化过程中设置 DDR2 驱动器的阻抗和电压电平。它的重要性体现在以下几个方面:

- OCD 通过最小化数据选通 (DQS) 到数据 (DQ) 的偏差来提高信号质量。

- 它通过最大限度地减少过冲和欠冲问题来提高信号质量。

- 它通过 IO 驱动器电压校准吸收来自每个 DRAM 供应商的工艺变化。

OCD 的驱动器阻抗调整引擎使用一种状态机:对此最基本的解释是,状态机是一种在任何给定时间存储组件状态的设备。

为了检测最佳内存设置,系统会根据不同的但预先确定的配置值发送多个测试信号。测试完成后,将使用提供最佳信号质量的值。最佳DQS波形可提供最大的数据眼图区域,同时将抖动、过冲和下冲降至最低。如果经过适当的调整和激活,它可以扩展系统时序裕度,从而有助于改善整体信号特性。JEDEC

的DDR2规范文档指出,如果不使用OCD校准,则在上电和初始化过程中将采用默认参数。一些制造商并不认为这是DDR2的必要功能,并且通常将其保留为默认值以节省设计成本和时间。这可能是导致某些DDR2 800MHz(及更快)内存出现问题的一个因素。

驱动性能/驱动强度和过渡时间 Drive Performance/Drive Strength and Transition Time

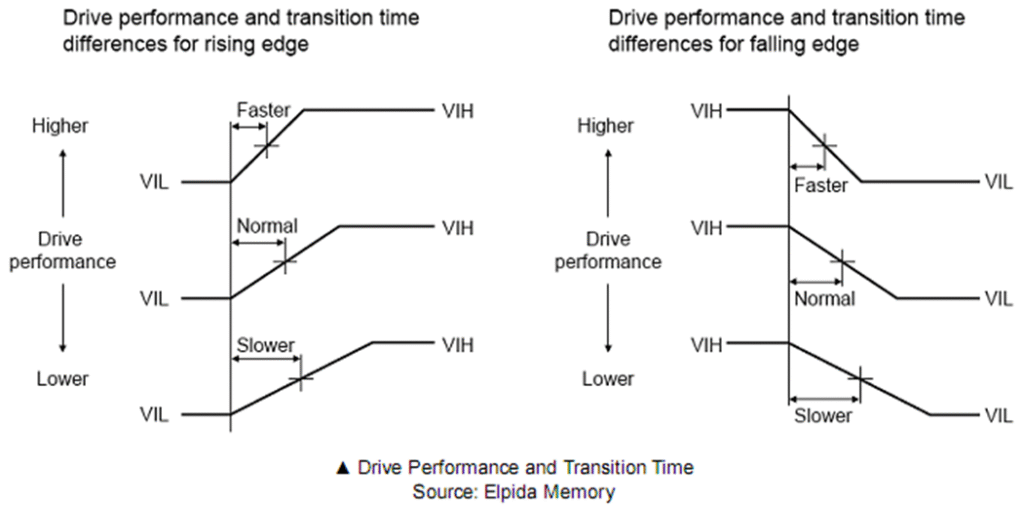

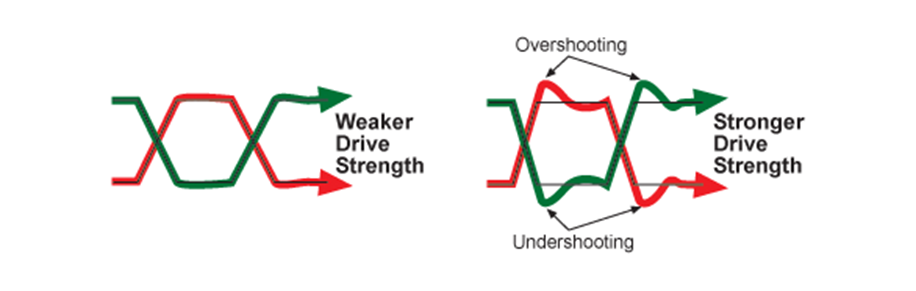

驱动器性能与转换时间成正比。驱动器性能越高,内存低电压状态和高电压状态之间的转换时间就越短(或越快)。驱动器性能有时也称为“驱动强度”或“边沿速率”。

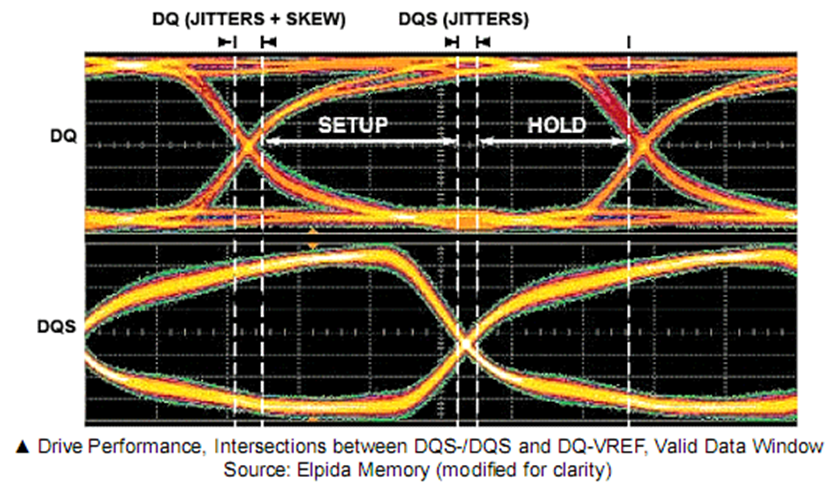

上图可以看到:驱动能力越强,信号的斜率越大,越快到达波峰/波谷

只有当电压上升或下降幅度设置在特定水平之间时,信号才能被正确读取。转换时间是指从低电压 (VIL) 变为高电压 (VIH) 状态或从高电压 (VIH) 变为低电压状态所需的时间。因此,转换时间越快,电压上升和下降的速度就越快。

更强的驱动性能会使波形上升部分的电压更快地上升。相反,它会迫使波形下降部分的电压更快地下降。需要注意的是,驱动性能功能应用于许多领域,通常来说,这个概念相当普遍,但不应将其混淆为特定设备或领域中单一因素的代表。

在某些主板中,内存子系统的许多方面都允许用户更改各种驱动强度值。将驱动性能设置过强可能会产生破坏性的过冲和下冲效应,从而与将其设置过低一样危及数据完整性。

想象一下一辆汽车上下坡:你把油门踏板踩得越深,汽车爬坡越快。同样,下坡时踩下踏板会使下坡更快。

这代表着汽车驱动性能的提升。那么,如果你过度增加驱动强度,到达山顶或山脚会发生什么?你会超过顶峰,四个轮子会离开地面,像好莱坞电影里那样飞过空中。这就是所谓的“超调”。

这同样适用于下坡,施加过多的驱动强度会导致惯性使你超调、失去控制并撞车。

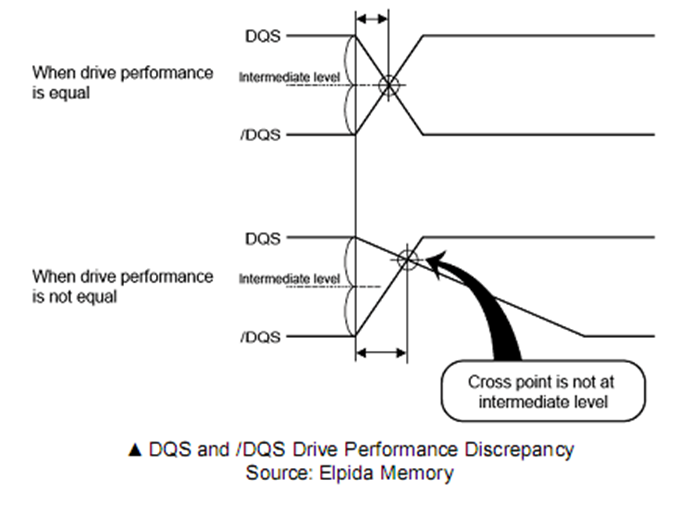

数据选通 (DQS) 驱动性能

当数据选通信号DQS和/DQS具有不同的驱动性能时,它们将具有明显不平衡的转换时间。

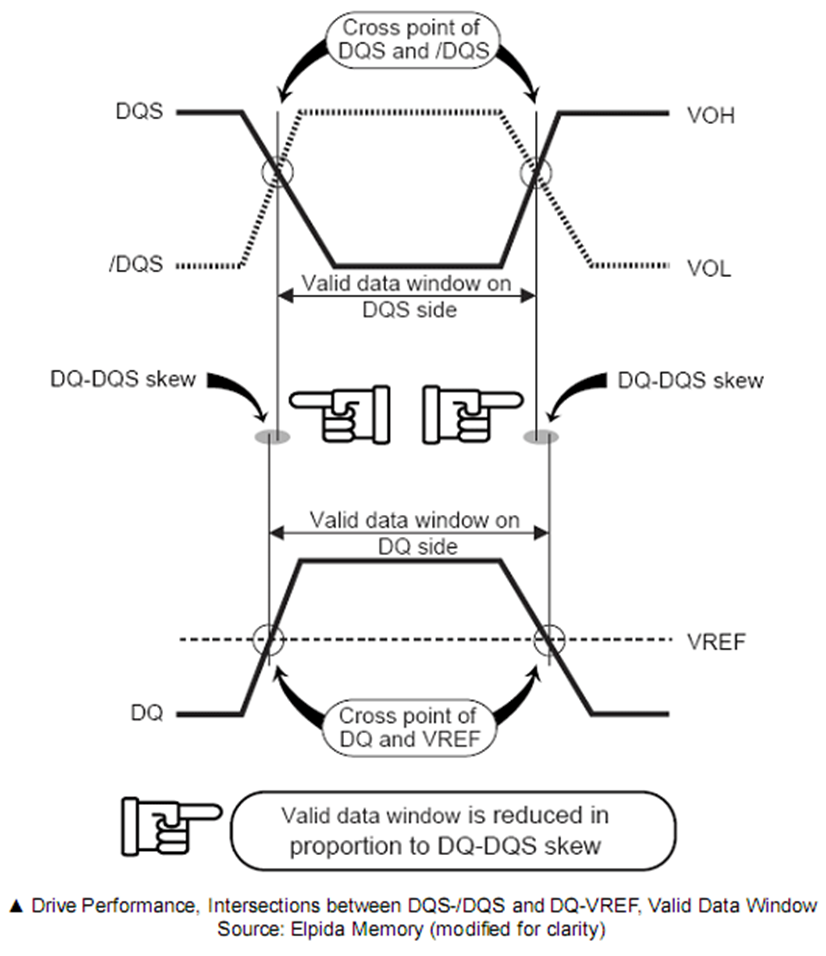

DDR2 采用差分数据选通信号 (DQS) 设计,使用 DQS 和 /DQS 信号之间的交点作为数据传输的参考。任何偏差都会对时序精度产生不利影响,并可能造成人为的 DQS-DQ 偏差。内存控制器将通过与差分数据选通信号 (DQS) 同步来移动数据 (DQ) 信号,而差分数据选通信号又会跟踪系统时钟。DQ

信号使用与参考电压 (VREF) 的交点作为参考,与 DQS 同步。为了实现最佳数据传输,DQS-/DQS 和 DQ-VREF 之间的两个交点必须对齐。因此,调整 VREF 有时可以提高故障系统的稳定性。然而,对于家庭用户来说,他们无法观察并确切了解正在发生的事情。

DQ-DQS 偏移效应会缩短内存控制器发送和接收数据信号的时间,从而导致数据眼和有效数据窗口减小:成功的信号传输需要足够的建立时间和保持时间裕度。DQ-DQS 偏移通常会对运行频率为 800MHz 或更快的 DDR2 内存模块造成不利影响。

总而言之,驱动器阻抗调整引擎和 OCD 校准电路用于调整 DQ 和 DQS-/DQS 的上拉和下拉驱动强度,以使 DQ-DQS 偏差尽可能小,从而以更大的冗余度扩展数据眼。