https://www.bit-tech.net/reviews/tech/memory/the_secrets_of_pc_memory_part_4/1

台式电脑的第三代 DDR 内存模块 (DDR3) 于 2007 年中期首次推出。与 DDR2 一样,台式机 DIMM 使用 240 针连接接口,DDR2 和 DDR3 模块之间唯一明显的外观差异是 DIMM 的 Key-Notch 位置。

几乎所有的台式机 DDR3 模块都采用细间距球栅阵列 (FBGA) 封装,其形状根据制造商不同,有方形的,也有略呈矩形的。FBGA 封装实际上可以容纳比实际所需更多的引脚,因此,一些设计师和工程师长期以来一直期盼的功能,例如异步复位 (RESET),最终获得了 JEDEC 的批准,并成为规范的一部分。

顺便多说一下同步复位和异步复位。步复位就是指复位信号只有在时钟上升沿到来时,才进行复位。相比之下,异步复位是指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。【参考】:https://www.zhihu.com/question/20280893

二者相比,异步复位比同步复位具有一些关键优势,主要与某些设计环境中的速度和简单性有关。 它们可以立即复位电路,与时钟信号无关,并且不需要专用时钟信号即可使复位生效. 这在需要快速、立即复位的系统中尤其有用,例如上电时或响应错误情况时。

更具体来说:

- 更快的重置响应:

异步复位可以立即置位复位信号,而无需等待下一个时钟周期。 这在需要立即复位的场景(例如上电或错误恢复)中至关重要。

- 无时钟依赖:

异步复位不依赖于时钟信号,这意味着即使时钟未运行或不稳定,它们也可以复位系统。 当系统在初始启动期间可能没有可靠的时钟源,或者时钟被暂时禁用时,这非常有用。

- 在某些情况下更简单的设计:

在即时复位功能至关重要的设计中,异步复位可以简化设计流程。 例如,异步复位可以减少复位信号和时钟之间精确时序同步的需求,从而简化时序分析和设计。

- 无论时钟如何,均保证复位:

异步复位确保系统复位而不管时钟的状态如何,这在启动时非常重要,因为此时时钟可能尚未运行或者时钟不稳定。

总之,与同步复位相比,异步复位提供了更快、更直接的复位能力,并且在复位期间可能无法获得可靠时钟或立即复位至关重要的设计中特别有用。

从上面可以看到,DDR3 使用异步复位应该是为了更容易实现。

虽然许多 DDR3 DRAM 基于 95nm 制造技术,但镁光科技的 78nm 工艺已从其 DDR2 D9 系列转移到 DDR3。镁光科技计算部门高级营销经理 Brett Williams 最近告诉我们,镁光科技的 65nm 工艺已完成测试,并将很快用于 DDR3。虽然该工艺应该在今年上市,但在 DDR3 生命周期结束时,我们应该会看到更精细的、更接近 45nm 水平的制造技术。

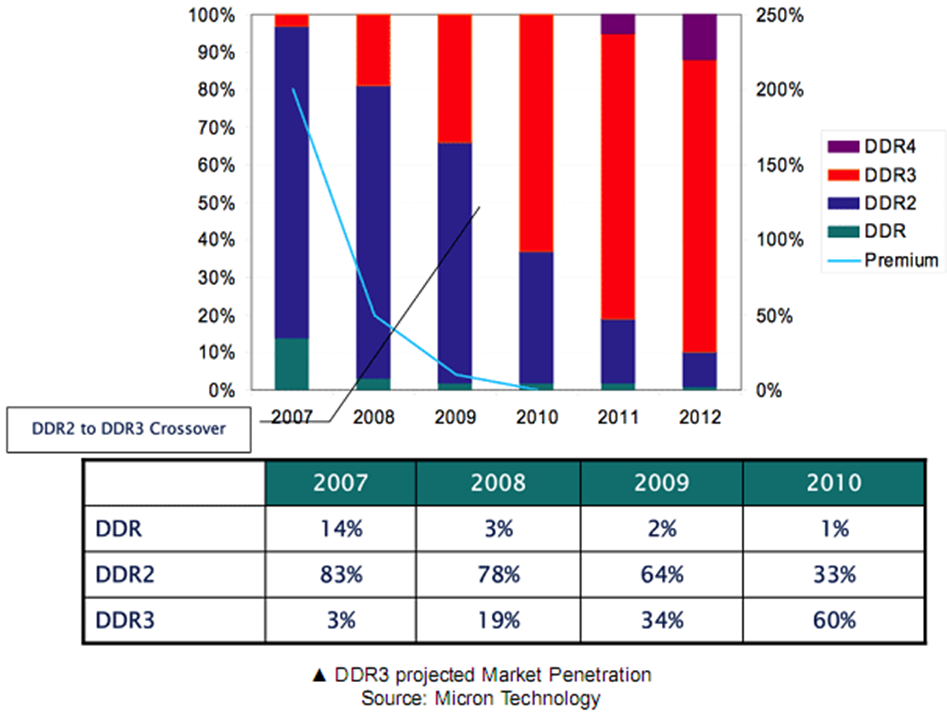

据镁光科技 (Micron Technology) 预测,DDR2 到 DDR3 的市场份额将在 2009 年上半年达到 50% 的临界点,而各大 DRAM 制造商的 DDR3 产量大幅提升预计最早也要到 2008 年第三季度,但更有可能是在 2008 年底。

这将导致价格在 2009 年之前维持高位,至少就 DDR2 的密度和成本而言是如此。OCZ、Corsair 和 Super Talent 等高性能模块制造商已经宣布推出性能超过 1.8-2GHz 的 DDR3 模块,远远超过了 JEDEC 1.6GHz 的上限标准。

普通用户务必注意,这些高端模块尚未在各种主板上进行兼容性测试,而且即使只有极少数主板能够支持,也很容易宣称内存产品“能够”达到这种速度。这些只是为了制造营销噱头,让公司品牌出现在新闻和人们的脑海中。DDR3模块的容量可达 16GB 甚至更高。相比之下,DDR2 模块的容量峰值预计为每个模块 4GB,但与 1GB 和 2GB 模块相比,这种容量将格外稀有且价格昂贵。随着 AMD AM3 处理器和英特尔下一代 Nehalem 处理器的推出,DDR3 的普及预计将加快步伐,届时整个处理器市场将采用支持 DDR3 的集成内存控制器。

DDR3 功耗降低

DDR3 的优势包括更低的功耗、更快、更大的容量以及改进的信号完整性管理功能。

每代 DDR 的电压要求都在降低,从 DDR1 的 2.5V、DDR2 的 1.8V 到 DDR3 的 1.5V,然而高频 DDR3 模块可能需要 1.8-2.0V 之间的任何电压才能稳定运行。

尽管默认电压为 1.5V,但我们预计某些 DDR3 模块的功耗要求甚至会更低;镁光科技的 Brett Williams 告诉我们,原始设备制造商 (OEM) 正在推动 DDR3 内存控制器的根本性变革,以允许低于 1.5V 的电压选项。预计将使用的移动设备(如笔记本电脑和超便携式计算机)需要此功能来满足日益严格的功耗和热预算。

一个重要点是,预计便携式设备将采用固态磁盘 (SSD) 和超低电压 DDR3。它们的综合效果令人惊叹,因为它们将显著降低设备的散热和功耗,同时提升潜在性能。因此,我们可以期待运行温度更低的笔记本电脑,以及电池续航时间更长的笔记本电脑。

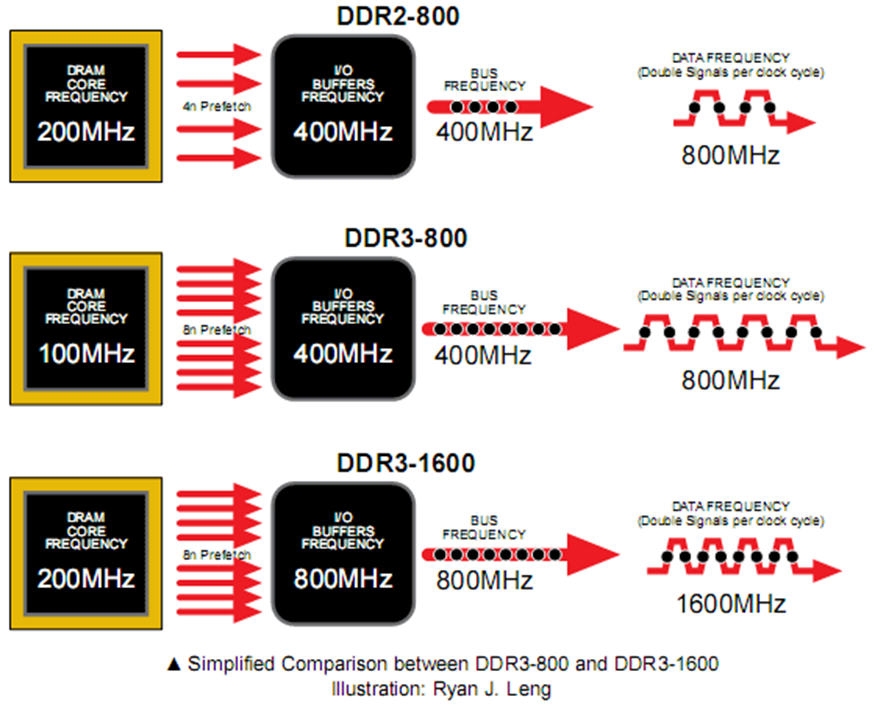

数据预取

DDR3 采用“8位 预取”技术(8-bit prefetch或8-n prefetchn代表芯片位宽),DRAM 在每个周期将 8 位(1 字节)信息从内部存储芯片组传输到 IO 缓冲区,然后再发送出去。这样的设计能达到令人惊奇的效果,DRAM 核心频率与 DDR1 相比几乎保持不变,而数据吞吐量却提升了 800%!这也充分证明了工程界的创造力。

在设计上保持与前几代产品相同的或更低的核心频率,对 DRAM 的制造良率和成本都有积极的影响:这关乎经济效益。高良率有助于降低 DRAM 的价格,进而影响消费者的响应速度,并促进更快的普及率。

与 DDR2 类似,DDR3 支持可编程的 4 和 8 突发(Burst)长度。然而,根据 8位预存取 规则,当使用 4 Burst长度时,连续读取或写入操作会在Burst之间产生间隙。因此,DDR3 引入了突发斩波命令,允许实时选择突发长度。

Burst 突发传输【参考1】

Burst(突发)是指在同一行中相邻的存储单元连续进行数据传输的方式。

Burst Lengths(突发长度,简称BL)指连续传输所涉及到存储单元(列)的数量就是突发长度。

在DDR3 SDRAM时代,内部配置采用了8n prefetch(预取)来实现高速读写。这也导致了DDR3的Burst Length一般都是8。当然也有Bursth ength为4的设置(BC4),是指另外4笔数据是不被传输的或者被认为无效。

参考:

1. https://zhuanlan.zhihu.com/p/582524766