继续 《PC 内存的秘密 第一部分》原文在 https://www.bit-tech.net/reviews/tech/memory/the_secrets_of_pc_memory_part_1/6/

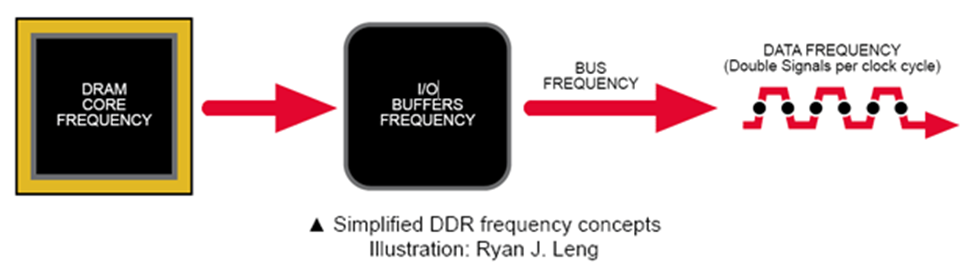

有几个独特但重要的速度概念需要牢记。它们是 DRAM 核心频率、输入输出 (IO) 缓冲区频率、内存总线频率和数据频率。它们用于描述内存系统不同部件的性能水平。

所有计算机内存模块都以数据频率为标称值。例如,DDR2-800 中的“800”数字描述了模块以 800MHz频率搬运数据的能力。另一方面,IO 缓冲区和总线频率将以 400MHz 运行,而 DRAM 核心频率仅以 200MHz 运行。

频率 (MHz) 和数据吞吐量 (Mbps) 之间的关系很简单。一个信号是 1 位数据:0 或 1。下图中的圆形黑色“操作点”。800MHz 数据频率意味着它将以每秒 8 亿次的速度发送 1 位数据,因此两者的乘积等于每秒 800 兆比特 (Mbps)。 (注:请记住,位和字节是不同的:8 位 = 1 字节,因此之前的 800Mbps 仅相当于 100MBps 或每秒兆字节)。

在给定数据频率的情况下,实际或有效数据吞吐量低于预期。例如,800MHz 的 DDR2 不会将该频率全部用于数据流。相反,命令和控制信号会占用部分数据。这有点像购买 160GB 硬盘,格式化后,只有 149GB 可用于数据。这是因为驱动器的一部分被系统级信息(如主引导记录 MBR 和分区表)占用。

对于一些爱好者和完美主义者来说,这是内存超频很好的理由,以使数据吞吐量更接近或超过 800MHz 数据流。使用指定为 1066MHz 的 DDR2 模块可以更好地实现这一点。

双通道和单通道模式

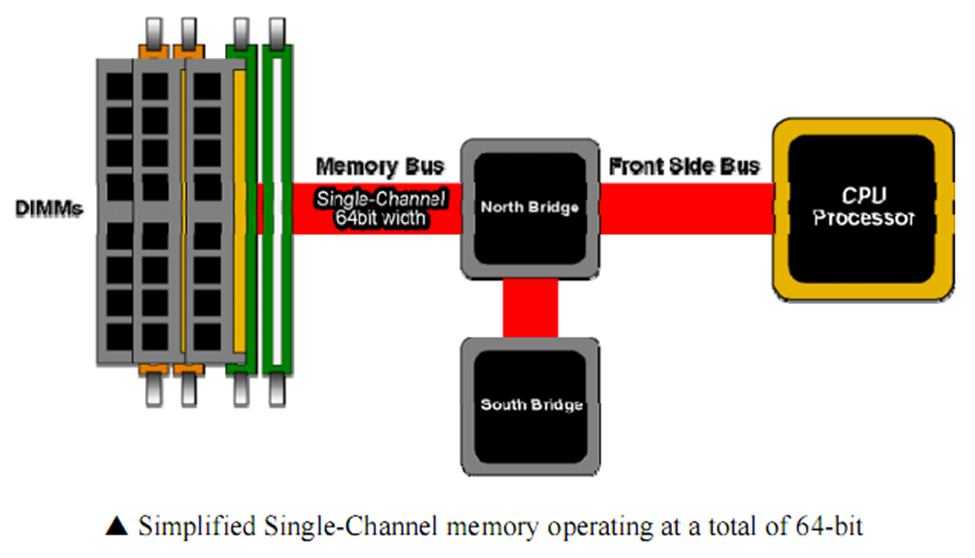

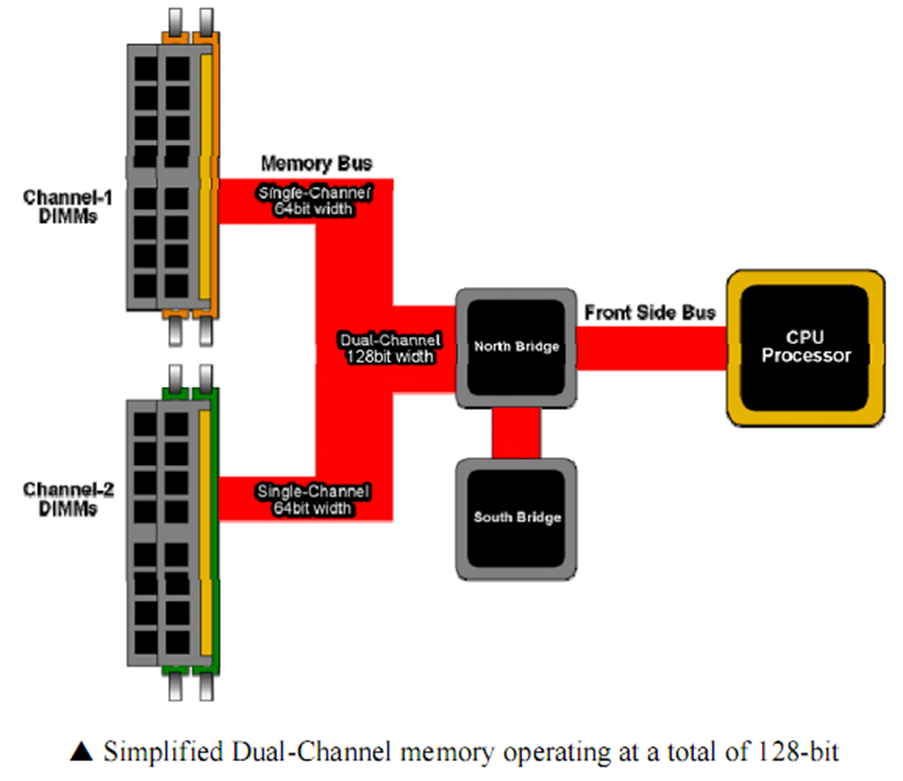

DDR 的另一项重大创新是能够使用双通道,而不是传统的单通道内存总线。这种设计极大地提高了内存性能。

在对称双通道芯片组上,将两个内存模块放在相同颜色的插槽中将自动为用户提供双通道性能,但是在 4 插槽主板上使用 3 个内存模块将使主板切换回单通道模式。非对称双通道芯片组能够使用 3 个 DIMM 在双通道模式下运行,从而始终有效地为用户提供 128 位内存性能。

当前基于台式机的 DDR 内存技术无法支持每通道超过 2 个 DIMM,但基于服务器和工作站的 FB-DIMM(全缓冲 DIMM)内存控制器(用于英特尔 CPU)设计时考虑了每通道 8 个 DIMM。这些高端计算机通常配备四通道配置,需要至少四个 DIMM 才能使用它。

每个标准台式机内存模块支持 64 位数据总线,而基于服务器的内存模块每通道使用 72 位数据总线:额外的 8 位用于纠错码 (ECC)。由于增加了额外的性能和纠错特性的复杂性,R-DIMM 和 FB-DIMM 比台式机使用的内存贵得多。

CPU 和带宽增长

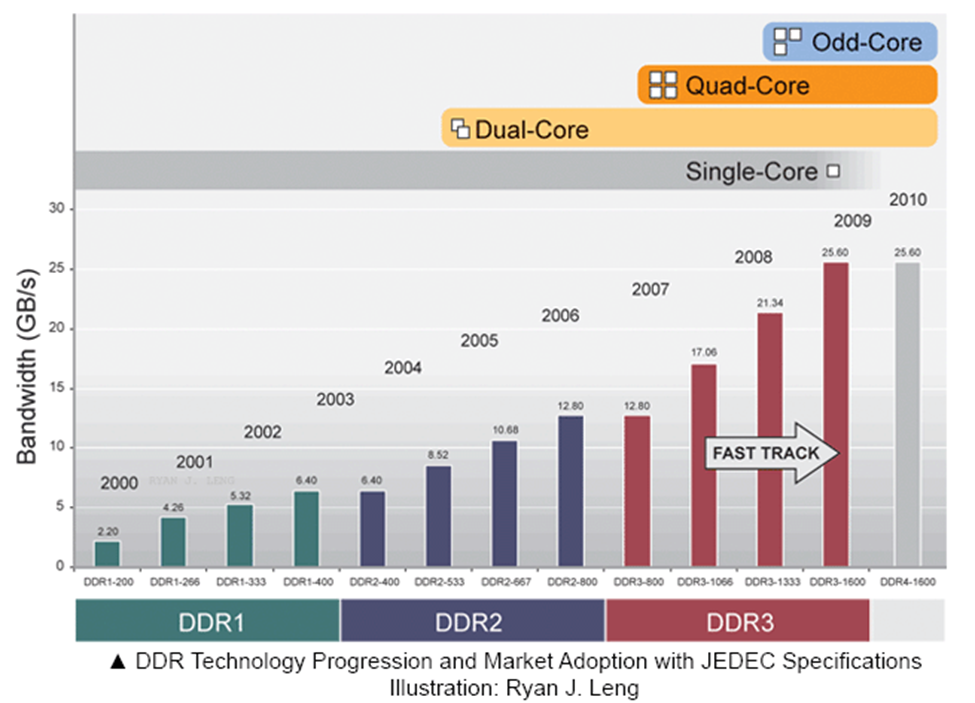

内存系统与 CPU 的演进有着直接的关系。随着更强大的处理器进入市场,需要更多的内存带宽来跟上 CPU 的处理速度。较慢的内存系统无法向快速的 CPU 提供足够的数据,这会导致处理器花费更多的时间在等待更多数据。内存系统的目标是在尽可能短的时间内为不同的任务存储和检索大量数据。如果没有同样快速的内存系统,CPU 将无法充分发挥效能导致效率低下。

下图说明了这一现象。摩尔定律描述 CPU 的处理能力每 18 个月翻一番。英特尔核心团队负责人 David “Dadi” Perlmutter 将其归类为“经济性和技术进步的简单关系”。计算机的效率在很大程度上依赖于内存系统来跟上 CPU 方面的改进。

单核 CPU 过去只是通过提高处理频率来提升性能。2004-2005 年,一种新的台式机 CPU 设计将处理器改进的动态从原始速度的单一因素转变为两个因素:处理速度以及核心数量。

此后的 CPU 性能提升依赖于核心频率的改进、处理器封装内的核心数量、具有更先进的预测和预取优化的缓存技术以及改进的总线效率以避免瓶颈。用于内存访问的数据预测和预取算法对处理器效率有重大影响。其他因素包括 L1、L2(和 L3)缓存的使用方式及其相关算法和访问分配。

第七章 EMI和内存控制器

由于内存速度从未真正能够跟上 CPU 性能,内存系统设计人员一直在使用多种手段改进性能。出于成本考虑原因,设计的主要目标一直是尽可能降低制造成本。

创新的设计人员没有选择提升内存的原始速度,而是通过并行访问的方法来提升整体速度。这些创造性的技术包括:双倍数据速率技术(DDR)、双通道或四通道模式(Dual or Quad Channel Modes)以及预取技术(Pre-fetching )等等。

需要特别主意的是,DDR DRAM 在技术工程角度存在成本限制,核心频率限制在 200MHz时整体成本最优。提升芯片外部总线传输频率相较于提升 DRAM 核心频率成本上要划算的多。

而为了达到上述目标,主板和内存模块必须在精确的信号管理和电磁干扰(EMI)控制机制方面取得设计和制造突破。因此,内存改进不仅仅是 DRAM 设计人员考虑的问题,也是从 CPU 架构师、芯片组和 DRAM 设计人员到主板和内存模块制造商的全行业协调努力的结果。

内存控制器

内存控制器的职责是对内存模块发送命令、管理内存模块和路由信号到内存模块。每个 DRAM 通常有四个或八个内存组,访问方式与 Microsoft Excel 工作表类似:有行和列。每当 CPU 需要读取或存储数据时,它都会通过内存控制器将信息发送到 RAM。

英特尔今年已经以 P35 和 X38 芯片组的形式发布了“Bearlake”3 系列家族下的第一代 DDR3 主板。Nvidia 和后来的 AMD 为其自己的 CPU 推出的未来芯片组也将在 2008 年支持 DDR3。当前的 DDR2/DDR3“组合”主板能够支持现有的 DDR2-800 或新的 DDR3-1066/1333 内存模块,但不能同时支持两个标准。DDR2 和 DDR3 使用不同的内存插槽,因为它们具有不同的模块键槽位置。

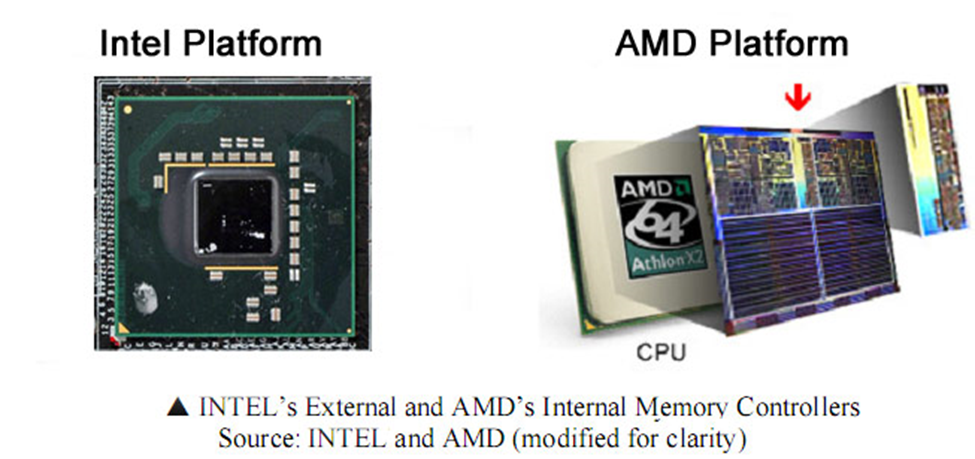

Intel 从Nehalem架构(45nm)开始整合了内存控制器(Integrated Memory Controller,IMC)。现在市面上的Intel处理器都已经整合了IMC。

将内存集成到 CPU 封装中的直接经济效益是降低该特定平台的主板制造成本。技术效益是减短CPU 对内存传输数据路径。集成内存控制器消除了对物理前端总线 (FSB) 的需求。无需独立的内存控制器芯片,主板制造商的设计和测试过程变得更简单 : EMI 问题更少,整个系统本耗设更低。理论上,这种设计消除了前端总线(FSB)带来的带宽瓶颈,可以显著提高内存性能。

集成内存控制器的缺点是它占用了处理器芯片上的空间,而这些空间原本可以用于更大的 L1、L2 和 L3 缓存。此外,任何直接内存访问 (DMA) 都必须经由 CPU 才能进入内存,这会为需要快速访内存的其他组件(如显卡)带来额外的延迟。

讲一个好玩的,我入行的时候是在昆山的微兴做台式机主板,偶然发现 Intel 的内存兼容性要比 AMD 好多了。发现的原因是当前公司研发有一批DQA 人员负责测试。有时候项目到了后期,实在没有什么好测试的他们就会拿出来内存“扫”一圈。Intel 通常没啥问题,比如,上一次是两三个型号有问题,这一次仍然是这些有问题。但是 AMD 就麻烦了,这次扫出来的和上一次有问题的型号往往不同,让人无比头大。

后来稍微有点经验,对于有问题的内存通过 SPD 信息判断,然后升高电压来解决。万幸的是这种方法对于大部分问题都有效果。