原文在 https://www.bit-tech.net/reviews/tech/memory/the_secrets_of_pc_memory_part_1/8/

延迟

DDR 的每一代发展都提供了更快的数据速率和更高的容量,但其代价是稳定性和信号准确性的下降。因此,每一代 DDR 都需要适应更高的频率和更高的信号延迟。

延迟可以理解为为时间上的暂停或延迟。当 DDR 信号命令发生变化时,内存子系统需要在不同的内存命令之间暂停。这就像一列火车驶入车站,然后停下来让乘客上下车。

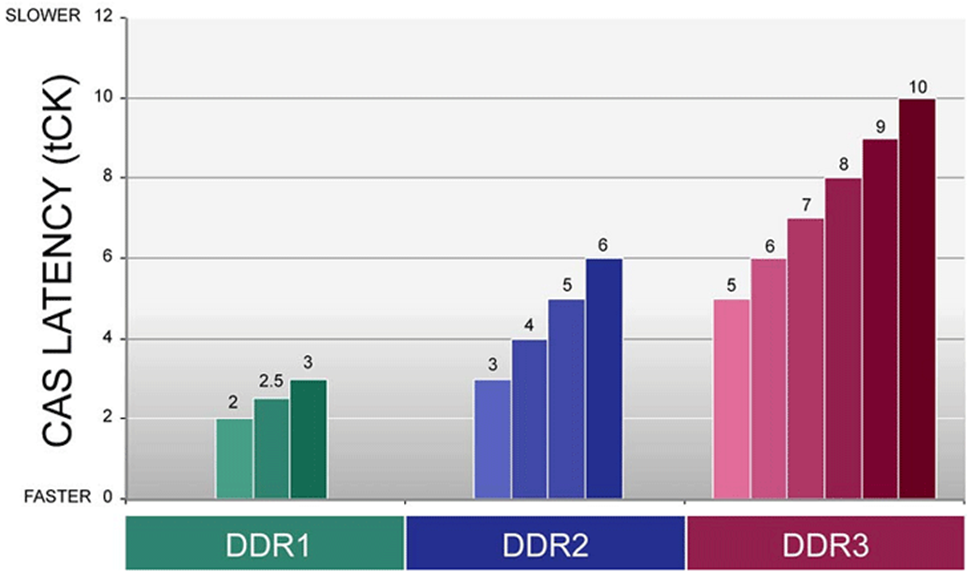

延迟有很多种类型。CAS 延迟通常被认为是最重要的延迟之一,然而随着 DDR 内存的更新换代,它本身的重要性逐渐降低,而多个延迟值的组合则更为重要。许多内存模块将 CAS 延迟表示为“CL”或简称为“C”。例如,CAS 延迟为 3 个时钟周期的内存模块通常被标记为CL3 或 C3。相关知识将在后续文章中讨论。

演化过程 在更高数据吞吐量需求的推动下,DDR 相关的各种技术经历了一系列的演进,同时尽可能保持经济性。

提高内存数据传输频率面临的两大挑战是信号噪声水平和时序精度。这通常被称为有效数据窗口 (Valid Data Window , DVW)。有效数据窗口有时也称为数据有效窗口(Data-Valid Window,DVW)或简称为“眼图”。它是决定信号可靠性主要因素。

为了降低信号反射,。例如:DDR1 采用主板上添加终端电阻方法,DDR2 则采用片上终端电阻 (On-Die Termination,ODT) 方法。DDR3 进一步扩展了 ODT 技术,允许根据情况动态调整 ODT 值。结合各种信号校准技术,可以合理地管理数据完整性,从而实现更快的传输速率。所有内存模块和主板都需要在设计和后期生产过程中进行信号准确性测试和验证,以确保各种内置校准方案正常运行。

这里提到的信号反射指的是高速信号中的反射问题【参考1】https://blog.csdn.net/hs977986979/article/details/142762703

在硬件电路中,高频信号的反射是一个非常重要的现象。当电磁波在传输线上传播时,如果遇到阻抗不连续点(如传输线的末端、拐角、过孔、元件引脚、线宽变化等),就会发生反射。反射波的大小和方向取决于入射波的幅度、相位以及阻抗不连续点的性质。

反射现象会导致信号轮廓失真,产生过冲、欠冲和振荡等问题。这些问题会影响电路的性能和稳定性。为了减小反射,通常需要在传输线的末端添加适当的终端匹配电阻,以确保信号的完整传输。

为了实现更高的效率和更低的散热,需要降低内存电压。数据中心运营商、台式机和笔记本电脑消费者对低功耗计算机越来越感兴趣,原因包括更环保、更长的使用时间以及总体运营成本的降低。

现代数据中心使用大量空调来维持运行。例如,卢卡斯影业 (LucasFilm) 的数据中心在 32 台空调机组中使用了 25 吨冷却剂来维持其系统的运行。功率效率通常以每瓦性能来计算,因此在保持相同性能的情况下,瓦数的降低对行业来说都是利好消息。

计算机内存系统如果没有多年的预先规划和全行业协商,就不会发生重大的范式转变。成员们会将一次又一次的修订提交给像 JEDEC 这样的设计管理机构,然后由一个合作伙伴委员会监督整个设计和批准过程。

制造过程中涉及的制造和测试设备成本高昂,这极大地阻碍了变革,因为自动测试设备 (Automatic Test Equipment,ATE) 价格极其昂贵,通常每台设备的成本高达数百万美元。MOSAID Systems 的 Brad Snoulten 认为,主要挑战有两个:

- 内存制造商无力购买或更换价值数百万美元的测试仪来满足不断增长的生产或工程测试需求。

- 内存ATE供应商面临着设计经济实惠且能有效抵御长期淘汰的解决方案的挑战。内存裕度的不断下降和设备复杂性的不断增加加剧了这些问题。

进步是一个渐进的演变过程,而不会出现跳跃式的进步。

第九章 GDDR,QDR 和 XDR

如果您在过去三年内购买组装一个台式机,它很可能至少有一个 PCI Express 图形扩展接口。这些显卡拥有一种专用的 DDR,即图形 DDR (GDDR) 内存,容量从最小的几十兆字节到超过上千兆字节甚至更多。

GDDR通常用于对带宽要求极高的高性能显卡。需要主意它的架构与 DDR 截然不同, 在JEDEC 的规范中GDDR 与 DDR 标准分属不同规范。

最新的 GDDR 技术已发展到第五代,简称为 GDDR5。不同代之间的主要区别在于性能和带宽。与 DDR 相比,GDDR 具有更高的性能,但在制造成本和功耗方面也明显更高。GDDR3的工作电压为 2.0V,而 DDR3 的工作电压为 1.5V,额外的电压有助于 GDDR 更快地运行,但也使其更容易泄漏电流,从而产生更多热量。这与大型图形运算核心组合意味着显卡产生的热量通常比主板中的 CPU 和内存加起来还要多。

Nvidia 8800GT 上的奇梦达 GDDR3

GDDR 具有较宽的数据接口和更大的帧缓冲区。与 DDR 设备相比,显卡等 GDDR 设备的单位容量较低;这会导致功耗更高且价格更高。增加设备的 GDDR 显存容量会相应增加功耗和设备价格。

QDR和XDR

四倍数据速率 (QDR) 内存系统始于 1999 年,由Cypress 导体公司、IDT 和 NEC 共同开发。此后,包括美光科技、瑞萨电子、三星电子和日立在内的多家公司都以某种形式参与其中。

我们预计, QDR 内存取代 DDR 的可能性不高,最重要的原因是QDR无法实现低成本的量产。其次,此举相当于内存技术的一次重大转向,出于经济性和实用性的考虑,很多制造商对此非常反对。

虽然 QDR 的数据频率和有效数据窗口显著提高,并具有超低延迟,但其内存容量相对于 DDR 而言相对较低。当 DDR3 达到每模块 8GB 时,QDR3 内存容量标准仍然以 MB 为单位。QDR 架构是特地为高性能通信应用而设计。

Lattice半导体公司表示,与 QDR 相比,DDR 技术存在以下缺点:

- 写入和读取共享一条双向数据总线,因此总带宽与 QDR 架构相比减少了一半。这在写入与读取比例接近 1:1 的情况下意义重大。

- 刷新需要中断数据传输。

- 访问延迟相对较高。

- 需要在上电后进行初始化,并在访问之前/之后激活/预充电行(内存接口简化了这一点)。

值得注意的是,目前市场上已经有了QDR内存甚至ODR内存(Octal-Data Rate)。索尼 PlayStation 3 采用 Rambus 的 XDR(极限数据速率)设计,该设计能够在每个时钟周期发送 8 位数据,而 DDR 只能在每个时钟周期发送 2 位数据。三星、奇梦达、尔必达、IBM、东芝、AMD 等公司目前都采用 XDR 设计。这些内存系统价格极其昂贵,而且不像 DDR 那样普及。

有一种罕见的 DDR2 类型,称为 DDR2+(或增强型 DDR2),其核心频率可达 333MHz,而 DDR2 标准频率为 200MHz。DDR2+ 也是由 QDR 联盟联合开发的。

下次我们将研究移动 DDR 和底层 DDR 技术,如温度补偿自刷新、部分阵列自刷新、深度断电和时钟停止模式以及 DRAM 封装和堆叠技术。

======================================================

讲个好玩的事情,三星内存的“反周期策略”:

三星充分利用了存储器行业的强周期特点,在价格下跌、生产过剩、其他企业削减投资的时候,逆势疯狂扩产,通过大规模生产进一步下杀产品价格,从而逼竞争对手退出市场甚至直接破产,世人称之为“反周期定律”。

在存储器这个领域,三星一共祭出过三次“反周期定律”,前两次分别发生在80年代中期和90年代初,让三星从零开始,做到了存储器老大的位置。但三星显然觉得玩的还不够大,于是在2008年金融危机前后,第三次举起了“反周期”屠刀。2007 年初,微软推出了狂吃内存的Vista操作系统,DRAM厂商判断内存需求会大增,于是纷纷上产能,结果Vista 销量不及预期,DRAM 供过于求价格狂跌,加上08 年金融危机的雪上加霜,DRAM 颗粒价格从2.25 美金雪崩至0.31 美金。

就在此时,三星做出令人瞠目结舌的动作:将2007 年三星电子总利润的118%投入DRAM 扩张业务,故意加剧行业亏损,给艰难度日的对手们,加上最后一根稻草。效果是显著的。DRAM价格一路飞流直下,08年中跌破了现金成本,08年底更是跌破了材料成本。2009年初,第三名德系厂商奇梦达首先撑不住,宣布破产,欧洲大陆的内存玩家就此消失。2012年初,第五名尔必达宣布破产,曾经占据DRAM市场50%以上份额的日本,也输掉了最后一张牌。在尔必达宣布破产当晚,京畿道的三星总部彻夜通明,次日股价大涨,全世界都知道韩国人这次又赢了。至此,DRAM领域最终只剩三个玩家:三星、海力士和镁光。尔必达破产后的烂摊子,在2013年被换了新CEO的镁光以20多亿美金的价格打包收走。20亿美金实在是个跳楼价,5年之后,镁光市值从不到100亿美元涨到460亿,20亿美元差不多是它市值一天的振幅。

上述来自雪球 作者:潇潇小鱼 链接:https://xueqiu.com/2691707350/179978325