https://www.bit-tech.net/reviews/tech/memory/the_secrets_of_pc_memory_part_3/7

同步存储器中的时钟偏差

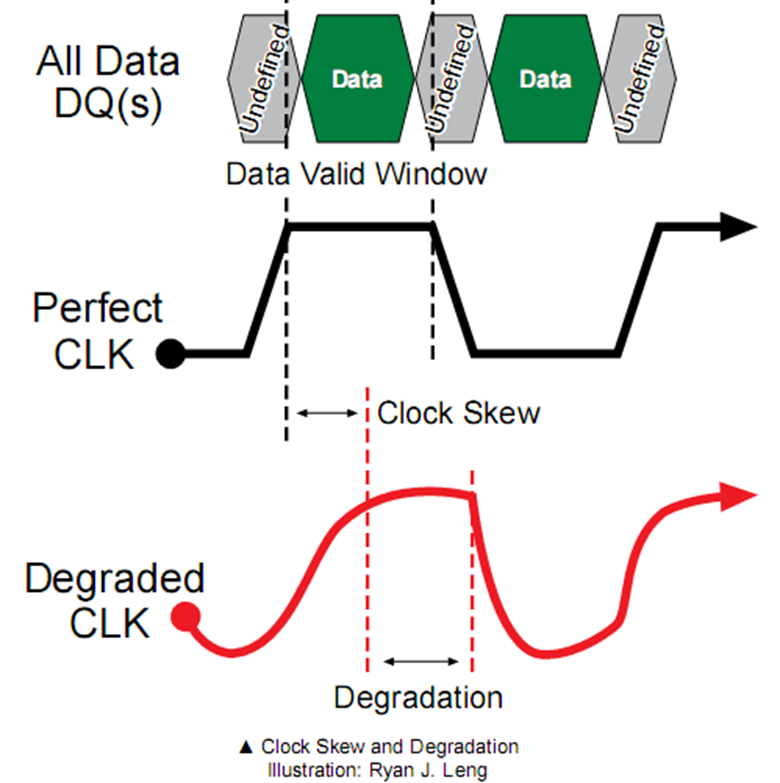

当越来越多的电路与一个时钟同步时,可能会出现时钟延迟现象。结果,所有数据都无法与正确的时钟关联并准时到达:这种现象通常称为“时钟偏差”。

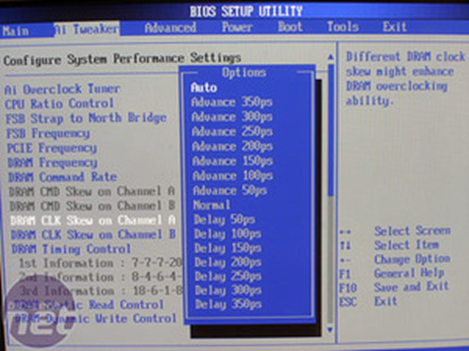

华硕 P5E3 Premium BIOS 中的“AI Clock Skew”选项

时钟偏差可能由多种因素造成,包括路径延长、温度波动、沿该线路添加多个逻辑电路、材料缺陷以及主板上的根本设计缺陷——换句话说,它可能发生在内存系统的许多不同部分。在不同位置消除偏差逻辑将尝试最大限度地减少负面影响,以保持数据和系统时钟之间的一致性关系。然而,随着内存性能的不断提高,并非所有问题都能轻松解决。

发烧友可能更熟悉主板 BIOS 中恰如其名的“Clock Skew”变量,它可以用于在超频计算机内存时获得更高的稳定性,从而解决 DIMM 之间的时钟偏差。不可避免的是,内存性能越高,出现时钟偏差的可能性就越大。

当主板上使用四条内存条而不是两条内存条时,时钟偏差会更加严重,偏差量取决于同时使用哪两条内存条,以及 PCB 的基本设计。

经过大量设计仿真和测试,质量极高的主板通常能够很好地控制时钟偏差问题。然而,由于市场竞争压力巨大,产品生命周期缩短,许多存在缺陷的主板在没有足够测试时间的情况下就过早上市并大肆宣传,之后又在 BIOS 更新中尽可能地进行修补。日益复杂的主板芯片组和更高的内存速度也增加了这方面出现故障的可能性。

单端差分选通到差分选通架构

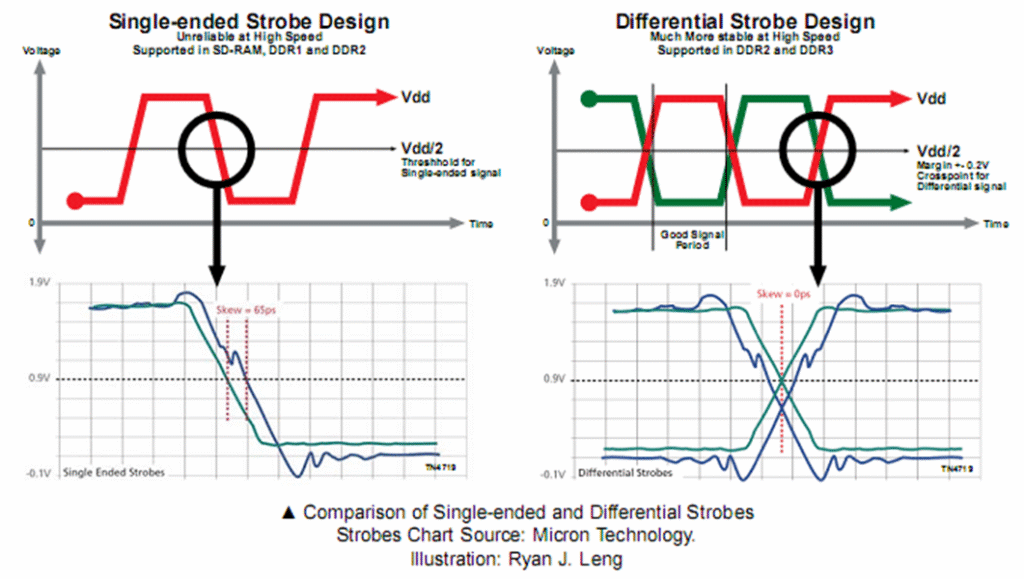

虽然单端数据选通信号最初用于 DDR1,但 DDR2 是支持单端和差分选通信号的演进转折点。最基本的解释是,单端选通信号依赖于一个振荡波,而差分架构则使用两个相互交织、交叉的反向振荡波。

镁光科技的 Aaron Boehm 强调,“差分时钟和选通信号方案对串扰引起的变化不太敏感”,而对于高速 DDR2 和 DDR3 来说,使用差分设计至关重要,Boehm 解释说,“随着我们不断降低 DRAM 电压并不断提高速度,降低时钟和选通信号对此类噪声的敏感度至关重要。 ”

对于单端选通信号设计,任何少量的噪声和干扰都会导致选通信号沿水平电压阈值(有时也称为参考电压电平)向左或向右偏移。这种水平偏移是有害的,因为它代表了时间的变化,从而导致了时间的不准确性。

存储器依赖于“相交”参考点的稳定性才能可靠地进行读写操作。差分选通脉冲设计更加稳定,因为波形异常只会导致相交中心点上下移动,这代表参考电压 (Vdd/2) 的变化,而不是时序偏移(左移或右移)。波动的电压阈值不如时间偏移严重。

在同步存储器系统中,任何显著的时间偏移都是致命的,因为这意味着数据不再与时钟一致,因此,只有这样的差分信号架构才能保证高速存储器正常工作。