PC 内存的秘密:第 3 部分

https://www.bit-tech.net/reviews/tech/memory/the_secrets_of_pc_memory_part_3/1/

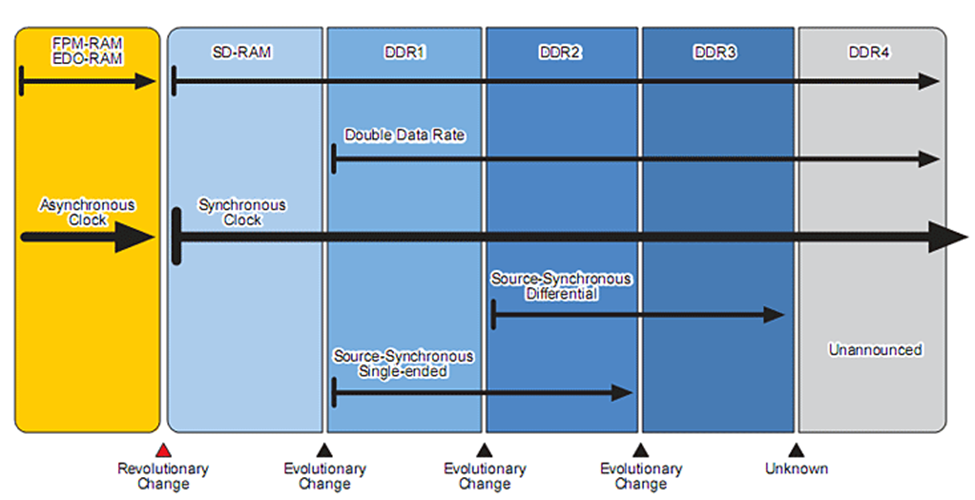

早期的内存技术基于异步时钟架构。异步内存包括快速页面模式 (Fast Page Mode ,FPM)内存、扩展数据输出 (Extended-Data-Out ,EDO) RAM 以及其他变体。顾名思义,这种内存不与系统总线时钟绑定或同步,因此这种设计存在根本性的局限性,导致总线运行速度无法超过 66MHz。美光科技计算部门高级市场经理 Brett Williams 表示,从异步时钟依赖内存到同步时钟依赖内存的转变是“一场革命性的变革,信号传输方式彻底改变…… ”。

LAB-Z注释:这里多提一下

内存同步

所谓内存同步,就是内存频率与CPU外频运行在同一频率。也就是说,在内存同步的情况下,内存频率=CPU外频。比如当200MHz外频的 P4 520与内存同步时,内存也运行在200MHz外频上。由于使用的是DDR内存,所以内存的频率=200MHz×2=400MHz(DDR400)。

内存异步

内存异步技术则是让内存频率与CPU外频不同,内存频率=CPU外频×N/M(特定的一个比值)。200MHz外频的P4 520在内存异步时,内存可以运行在166MHz,使用DDR333内存就可以了。当然,内存也可以运行在266MHz,此时系统只需要使用DDR533 内存即可。也就是说,N/M的比值可以大于1也可以小于1,即内存异步时,内存的频率可以高于或低于CPU外频。

存在原因

在早先的计算机系统中,内存和CPU之间的搭配,CPU处于主导的地位,也就是说当CPU的主频为100MHz,那么内存的频率就只能是 100MHz,内存的使用完全依赖于CPU。随着CPU技术的迅速发展,CPU的频率不断提高,这样就造成了用户升级CPU时就必须也对内存进行升级,无疑增加了升级的成本,这种情况直到VIA的694X芯片组发布之后才有所改变,内存与CPU外频终于可以实现异步运行了。

当然这样的异步运行技术并没有完全脱离CPU外频的束缚,而是采用了“±33MHz”的解决方案。也就是说,当P3处理器运行在100MHz 外频下,内存可以异步运行在133MHz或66MHz两种频率下。内存运行在133MHz频率的时候,系统就可以获得更大的性能提升,在当时绝对算得上领先的内存技术。至于现今的内存异步技术,已经发展到了更为先进的阶段。内存与CPU外频的异步运行甚至可以设定在4:3或5:4的比例状态下。

理论上来讲,搭配更高频率的内存就可以获得更大的数据带宽,对于系统性能的提升也会有很大帮助。并且内存异步技术还可以更为灵活的搭配内存,在CPU外频不断提高的现今,内存异步技术更可以帮助升级用户节省下更换内存的资金。

理论上来讲,内存异步技术提升内存的频率后,相应的数据带宽也会明显提高,性能应该有所增强。但就异步技术开始出现时的测试成绩来看,内存异步技术的性能提升并不是特别明显,这是为什么呢?其实这是由于采用了异步运行方式后,虽然增加了内存的带宽,但同时也增加了内存的延迟。

比如,某处理器运行在100MHz外频下,其时钟周期为10ns。运用内存异步技术之后,内存可以运行在133MHz频率下,时钟周期为 7.5ns。当周期为7.5 ns的时钟周期结束时,周期为10ns的时钟周期还没有结束,那么前者就需要等待后者完成一个周期后才能开始下一个周期,这样就造成了内存的延迟,而延迟所带来的性能损失也直接导致了测试成绩的下降。这种情况发展到NF2芯片组尤为严重,NF2主板甚至只有内存同步时才能获得最优性能,内存异步技术在当时的AMD平台甚至成为了“鸡肋”。

不过事情总是有转机的,处理器的外频不断提高时,内存技术也跟着飞速发展。高频内存与CPU外频之间,使用异步后的延时越来越小,系统性能的提升也就越来越明显,这样使得内存在一定程度上摆脱了CPU外频对其频率的束缚。内存和CPU之间可以更加灵活自由地进行搭配,这样给用户留下很大可控制的空间,在很大程度上促进了超频技术的发展。当然了,对于那些升级CPU的用户而言,也可以留下以前的内存,只要开启主板的内存异步功能就可以实现平稳的过渡升级。

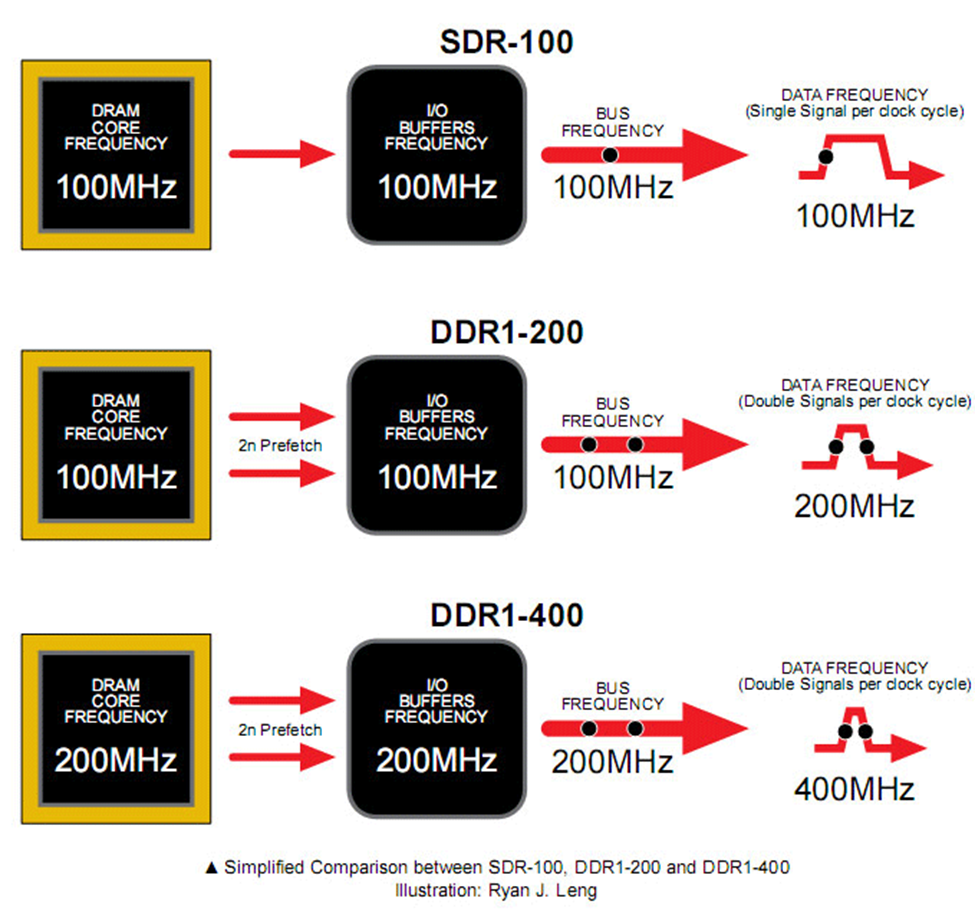

现代计算机内存仍然依赖于同步时钟设计,这种设计在同步动态随机存取存储器 (SD-RAM) 大规模市场采用后变得尤为突出。SD-RAM 起始频率为 66MHz,每个时钟周期限制为一个信号。后来,这种设计演变成了 DDR 内存,即双倍数据速率同步动态随机存取存储器 (DDR)。DDR 内存是一种 SD-RAM,能够在一个时钟周期搬运两次数据。

此时,重要的是要认识到,我们所说的“计算机内存”实际上是一组不可分割的子系统,包括 RAM 模块、主板、MCH(内存控制器中枢)以及 CPU。我们知道,有时 CPU 会将 MCH 集成到其设计中,例如 AMD 的 Athlon 64 和 Phenom 处理器。

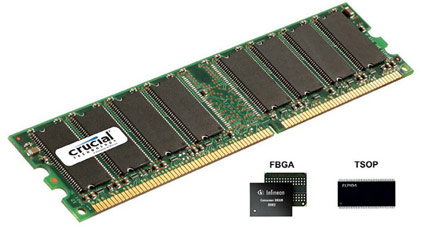

第一代:DDR1

第一代台式机双倍数据速率内存模块 (DDR1)采用 184 针接口设计,高于 SD-RAM 使用的 164 针接口。DDR1 通常基于薄小外形封装 (TSOP) 芯片,虽然也使用过一些基于球栅阵列 (BGA) 的 DRAM,但非常罕见。本系列第二部分中介绍过关于内存的封装。

TSOP 芯片的缺点是,由于两侧引脚向外延伸的特性,芯片会占用更大的 PCB 空间——这意味着密度较低。并且和 BGA封装相比,TSOP 在高速传输时也存在一些信号质量的问题。

图片的意思是 SDR 会在时钟上升沿传输一次数据,总线频率 100Mhz, 数据频率也是100Mhz;在 DDR 上,会在时钟的上升沿和下降沿分别传输一次数据,因此总线频率是100Mhz时,数据频率是200Mhz.

DDR1 DRAM 的最高工作温度通常在 85˚C/185˚F 左右,但有时也可能更低,具体取决于具体部件和制造商。理论上,与 DDR2 和 DDR3 中基于 BGA 的 DRAM 相比,采用 TSOP 芯片的 DDR1 模块可以承受更大程度的焊接温度而不会损坏连接引脚,因为焊点更大且更易于焊接。

一个内存模块的最高工作温度始终远低于 DRAM规格中所描述的数值,但这个因素会因内存芯片和印刷电路板 (PCB) 制造商以及所采用的热管理解决方案而异。

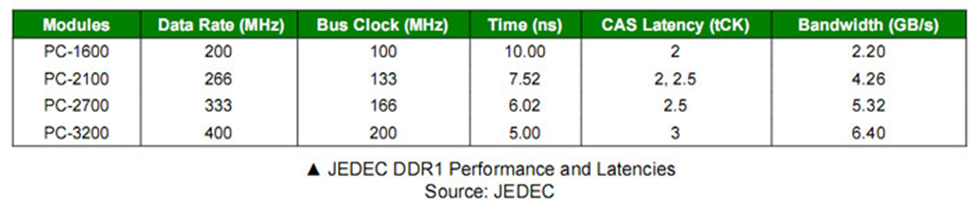

官方 DDR1 总线频率通常为 100MHz、133MHz、166MHz 和 200MHz,但偶尔也会有 150MHz、183MHz 甚至超过 200MHz 的频率出售给最终用户。由于DDR每个时钟周期可以附加两个信号,因此标准理论数据频率分别为200MHz,266MHz,333MHz和400MHz。

JEDEC 定义的 DDR1 电源为 2.5V,但一些制造商已认证其模块可在高达 2.8V 以上的电压下运行,且仍在保修范围内。这种额外的成本和购买保障对于系统超频爱好者来说非常实用。

源同步架构

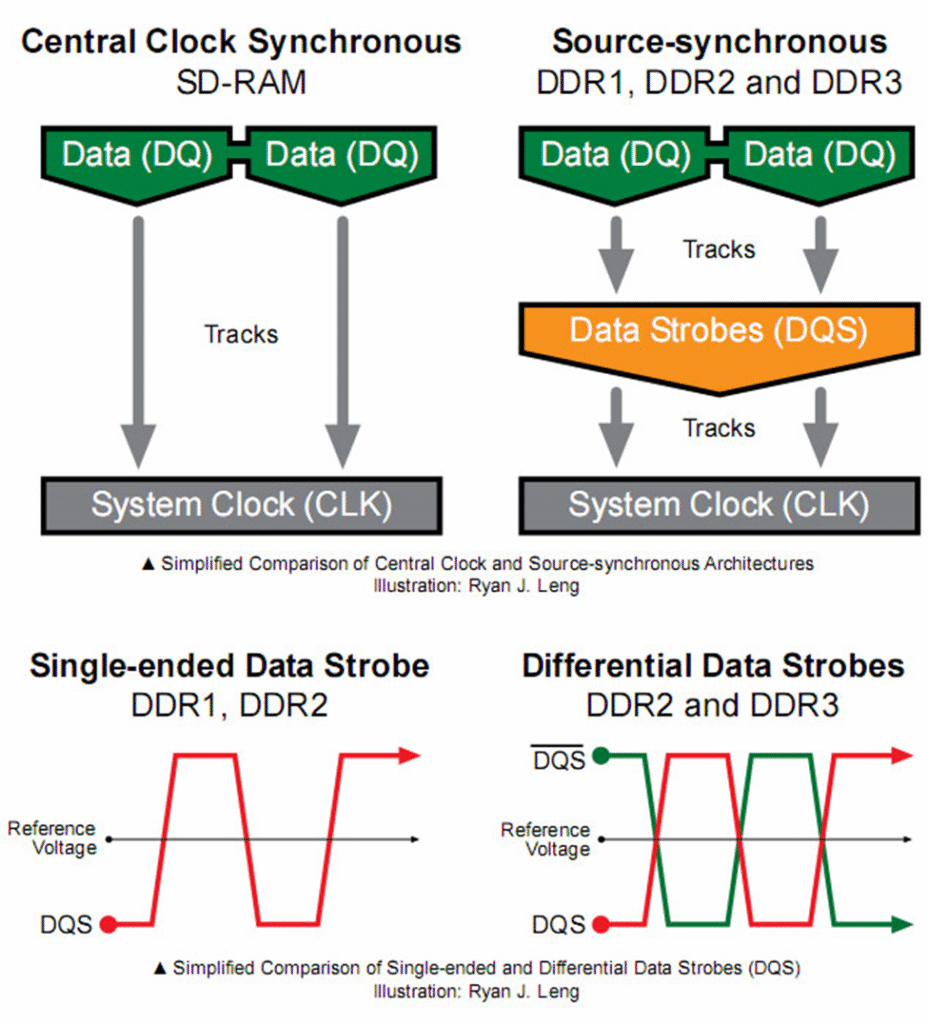

DDR1 中最重要的变化之一是不再依赖 SDR 中使用的中央时钟方案,而是引入了源同步或选通设计。

这样做的好处是可以提高性能。single-ended Data Strobe(DQS) 架构的引入在数据和中央系统时钟 (CLK) 之间创建了一个额外的跟踪层。

DDR1的“单端”(Single-ended)数据选通是指只有一个上升和下降信号波的特性(DDR2开始改成了差分信号)。该单端数据选通由数据 (DQ) 跟踪,以实现更有效的信号传输——它在容忍工艺-电压-温度 (PVT) 变化以及串扰、回声和信号反射引起的问题方面具有更大的基本强度,这些问题往往会扭曲波形或导致时序不准确。

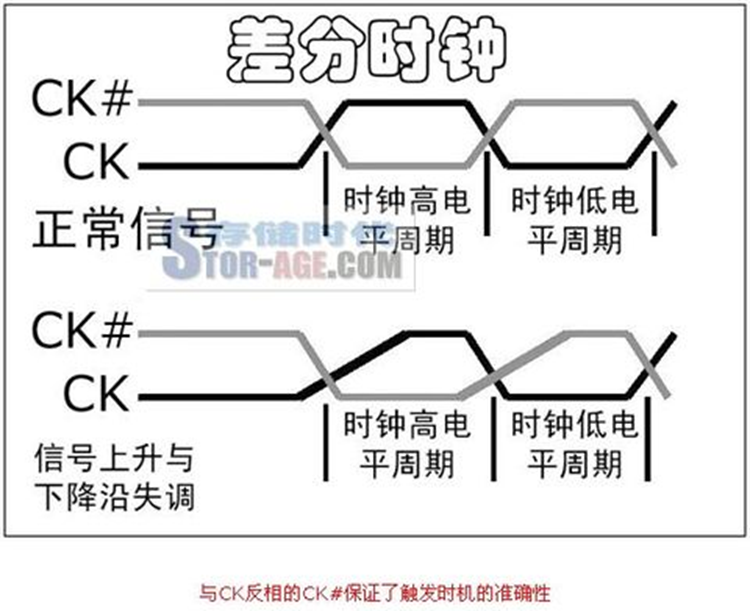

DDR2及之后的版本中,为了增强信号的抗干扰能力,尤其是对抗时钟信号的干扰,时钟信号如DQS和CLK等都被改为了差分信号。

引入一个称为数据选通的附加定时层的目的是帮助数据在更高速度等级下更有效地跟踪时钟;然而,这也带来了额外的复杂性。

前面提到的时钟信号改为差分信号,即出现了 CK和CK# 。引入的而原因是为了起到触发时钟校准的作用

由于数据是在CK的上下沿触发,造成传输周期缩短了一半,因此必须要保证传输周期的稳定以确保数据的正确传输,这就要求CK的上下沿间距要有精确的控制。但因为温度、电阻性能的改变等原因,CK上下沿间距可能发生变化,此时与其反相的CK#就起到纠正的作用(CK上升快下降慢,CK#则是上升慢下降快)。

而由于上下沿触发的原因,也使CL=1.5和2.5成为可能,并容易实现。【参考1】https://www.cnblogs.com/leaven/archive/2010/07/21/1782341.html

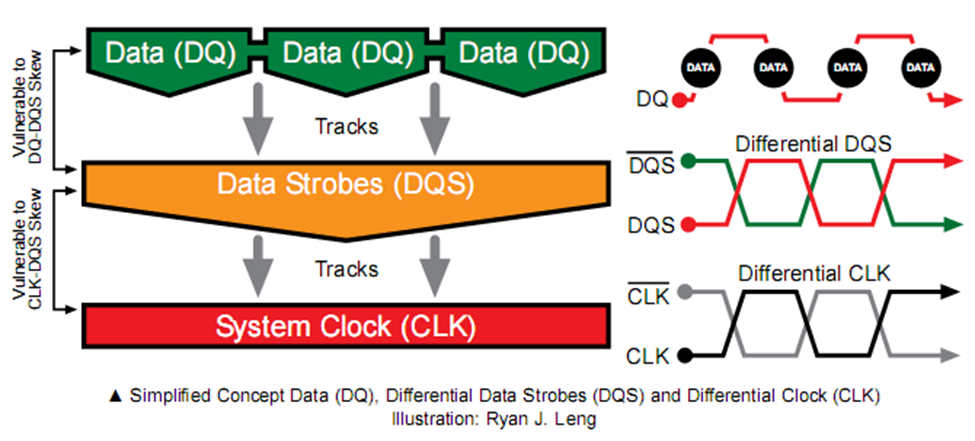

尽管数据选通可以缓解更高频率下数据与系统时钟之间的定时误差,但数据选通本身可能会与系统时钟不对齐或出现偏差。因此,必须在两者之间构建额外的“去偏差”或同步逻辑,以确保正常运行。

这个叫做数据选通或 DQS 的东西是什么?

数据选通信号 (SD RAM) 是数据相对于系统时钟的跟踪信号。它是一种振荡电信号,用于定义数据必须位于何处以及数据应在何处停留多长时间。

正如“同步”动态 (SD) RAM 的名称所暗示的那样,现代计算机内存依赖于所有部件按照集中时钟进行排列,以实现可靠的信号传输。它最初在 DDR1 中采用单端设计。在更高的 DDR2 速度下,需要采用差分选通设计。

美光科技应用工程师 Aaron Boehm 解释说,问题在于“时钟可能会有很大差异,因此 DQS 用于将所有数据与时钟对齐。在 DRAM 内部,选通脉冲跟踪时钟。因此,当 DRAM 输出数据时,数据会与选通脉冲对齐,而选通脉冲又跟踪时钟。当内存控制器写入 DRAM 时,数据集中到选通脉冲。数据选通脉冲 (DQS) 允许控制器和 DRAM 查看并锁定数据。 ”

关于为什么需要多增加一个 DQS 信号,有如下解释【参考2】

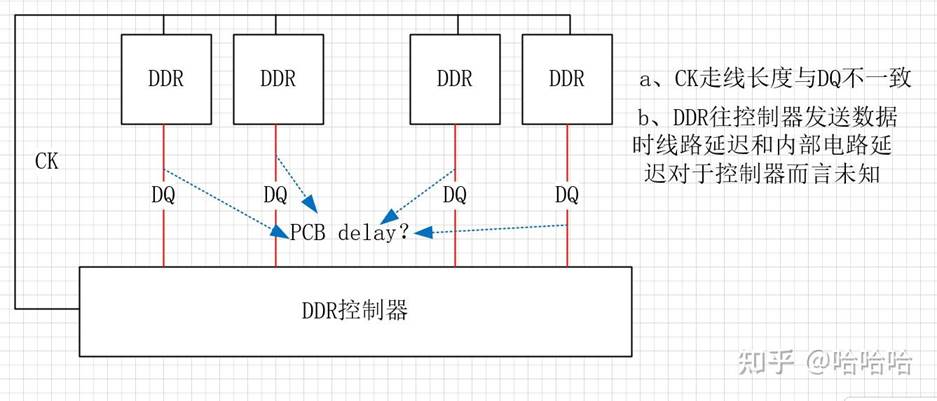

a、进行DDR拓扑,多个DDR芯片共同使用一个CK时钟,DDR控制器的数据总线可以以最短距离连接到DDR上去,但CK时钟需要进行分叉连接到DDR上去,导致CK走线比数据总线要长,若要想走线等长,那么需要数据总线做等长走线,数据总线的数量远比CK多,不利于PCB等长走线,所以不使用CK为基准。

b、当DDR向DDR控制器发送数据时,由于PCB走线和DDR发送电路的延迟对于DDR芯片而言不知道有多长,所以DDR控制器无法准确的通过CK对数据总线上的数据进行采样。所以不使用CK为基准

针对于以上两个问题,数据总线中引入了DQS这一信号,使用DQS做数据总线采样的参考时钟,因此DQS必须与DQ等长,DQS频率与CK一致,允许相位差,这个相位差(可提前可滞后)可以通过DLL调节,写数据时二者上升沿对齐误差允许0.75~1.25个时钟周期,读数据时的对齐误差以芯片的规格书为准。

【参考】

2.https://zhuanlan.zhihu.com/p/1896493235079193557