https://www.bit-tech.net/reviews/tech/memory/the_secrets_of_pc_memory_part_3/4

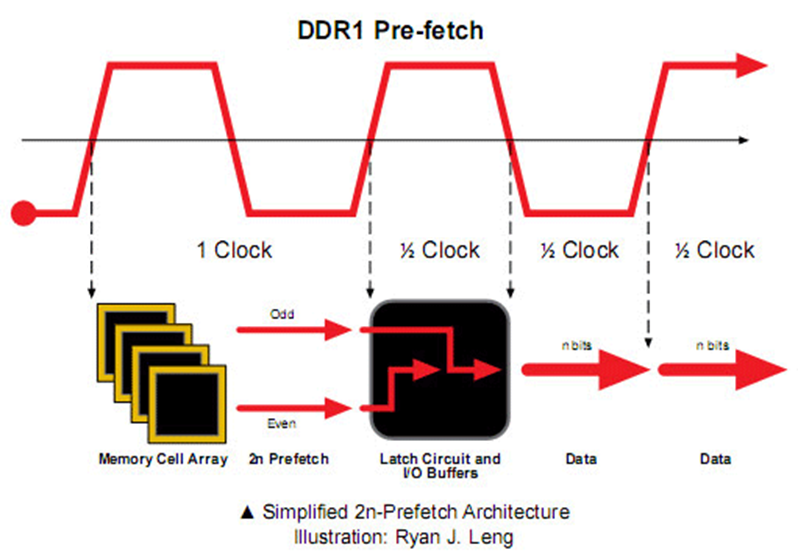

DDR1 采用“2n 预取”设计,这意味着在每个周期,内存模块会在 1 个时钟周期内从内存条中准备 2 位数据,然后将它们在 IO 缓冲区中背靠背排列,最后通过数据线发送出去。这种设计相当简洁而优雅:对于每一对,在信号波的上升沿和下降沿各发送一位数据,从而有效地将数据吞吐量翻倍,而无需提高 DRAM 核心频率。

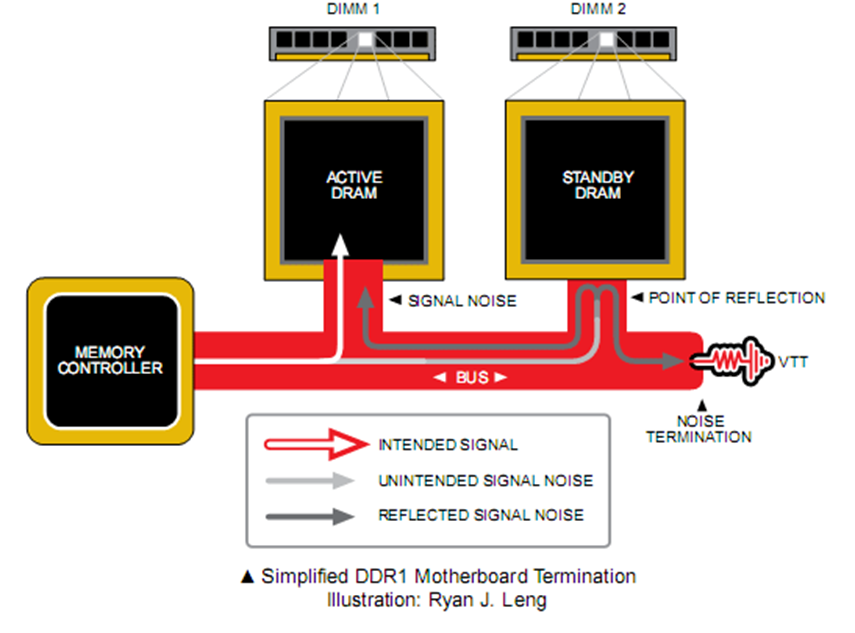

反射噪声管理

为了提高信号质量,主板的内存IO操作中内置了电阻终端,以消除信号反射引起的噪声。这种噪声是由信号从数据总线两端反射回来干扰新信号引起的。新信号与旧信号回声之间的冲突会引起抖动和相消干扰。信号可能会在阻抗不同的点发生反射,例如,内存插槽和内存条接触点。

需要注意的是,这种方法只能将噪声控制在DDR1设计性能参数范围内。超出该范围的噪声无法完全消除,甚至不足以造成稳定性问题。

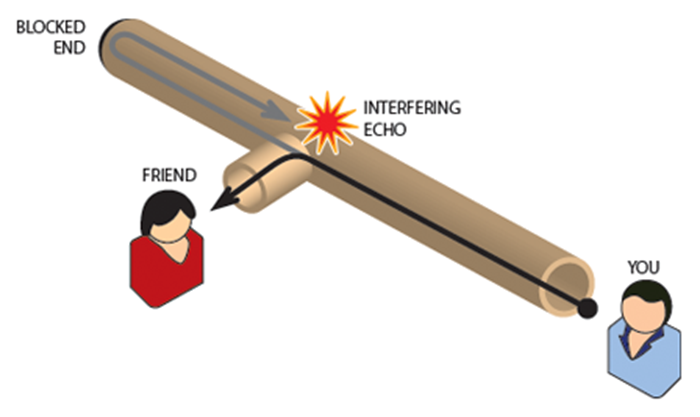

如何理解信号的反射问题

信号反射噪声类似于声音沿着一条长管传播,随后从封闭的一端反射回来,在那里你会听到回声。现在想象一下,在这条长管的中途,有一个开口,你的朋友正在那里听。当你沿着管道和朋友说话时,声音传到他们中间,继续传播到管道的尽头,最终以回声的形式反弹回来。

当你的朋友开始回复时,回声会干扰他们的信息。因此,听清回复会有点困难。随着你们说话速度越来越快,越来越难以跟上对话;这类似于在处理信号反射的同时提高内存频率。

一种解决方案是消音管道末端以吸收噪声——板载电阻终端的作用就是在反射回来之前吸收掉不需要的信号。